x1电压放大器或“缓冲器”是模拟设计的标准构建模块。本文介绍了一种元器件数量少的高性能分立式匹配晶体管缓冲器的设计,并涵盖优化其设计的一些细节。

在用一个运算放大器就可以轻松实现缓冲器的时代,为什么要使用分立电路?当高精度和最小空间不是特别重要的指标时,零件成本为50美分的双JFET放大器足以满足性能要求,它可提供数百兆赫的带宽,偏移误差仅10mV或更低,漂移为10μV/oC或更少。通过应用创新,分立元件电路也可以获得良好的性能,即使运算放大器过时仍然可以使用。缓冲器也可以成为设计库的一个重要部分。

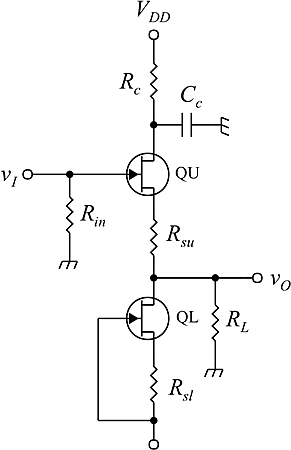

x1电压放大器的设计目标是实现这样的理想电压放大器:无限大的输入阻抗、零输出阻抗和线性度。为了实现高输入阻抗,使用JFET而不是BJT,如图1的缓冲电路所示。

图1:为了实现高输入阻抗,使用JFET而不是BJT。

离散JFET器件可从多家供应商获得,包括:

尽管单封装双器件(如2N3958、2N5196~2N5199,以及2N5564~2N5566等)在热跟踪方面具有优势,为降低成本,我们还是选择离散JFET器件。低端的双器件价格每个大约4.50美元,最好的则超过40美元。如果您可以承担额外的成本,可以选择价格贵的双器件,因为它们的热跟踪性能优于离散JFET。

设计缓冲器所需要的一些离散N沟道JFET的替代器件包括2N5484~2N5486。2N5485的成本约为每个0.20美元(批量采购数百个时)。其漏极电流的标称设计值在4~10mA规定范围内,中值为IDSS = 7mA(IDSS为ID@VGS = 0V)。此外,选择了两个JFET以便使用曲线跟踪器进行匹配。可以通过人工将它们分类为匹配的IDSS箱,每对花费不到一分钟的时间,产生的额外成本为0.10美元(按照美国劳动力成本计算)。

接下来,选择一些标准电源电压:VDD = +12V,VSS = -5V。这些电源电压在桌面电脑和仪器中都很常见。

匹配JFET的第一个设计特征是匹配晶体管的静态(dc)跟踪。如果底部晶体管QL的栅极连接到其源极,则VGS = 0V,漏极电流为IDSS。如果相同的电流通过QU(带有开路负载),那么由于它是匹配的,其VGS也是零,并且输入到输出之间没有电压失调。

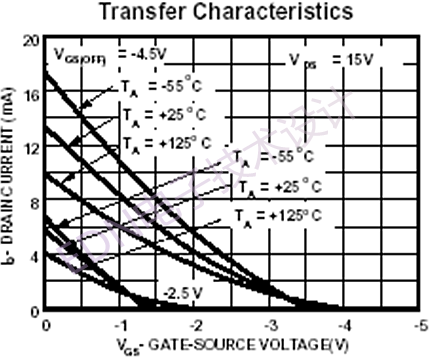

这一绝妙的设计技巧还可以通过将JFET工作点设置为零TC点来改善,其中具有给定ID的VGS的热漂移在整个温度范围内是最小的。对于JFET,零漂移VGS比夹断电压高约0.8V。VGSZ的值是各种温度的ID线相交的地方。对于2N5485,这大约为-1.2V,比-2V左右的夹断电压高约0.8V。2N5485(Siliconix)的曲线如图2所示。

图2:2N5485(Siliconix)的曲线图。

使用这些值,Rsl = Rsu = Rs = 1.2V/5mA = 240Ω,容差为5%。Rsl上的压降在波形路径中通过匹配电阻器Rsu上的类似压降进行补偿。为了更好地匹配,这些电阻的容差可以是1%。

随着输入电压的变化,两个JFET的功耗也会发生变化。功率的变化引起硅温度的变化,这会导致放大器响应中产生热感应电噪声或“热”。这种“噪声”与波形有关,最好视为热失真。通过设置JFET最大功耗的工作点(op-pt或偏置)可以使JFET的功耗最小,而无需改变输入(即在op-pt点)。功率的变化(我们希望最小化)在峰值功率附近最小,其中抛物线的导数值或斜率最小。

让JFET的工作点 - 静态偏置电流为I0。那么上、下晶体管消耗的功率为:

![]()

而且:

![]()

其中vL是RL上的负载电压。功耗的差为:

![]()

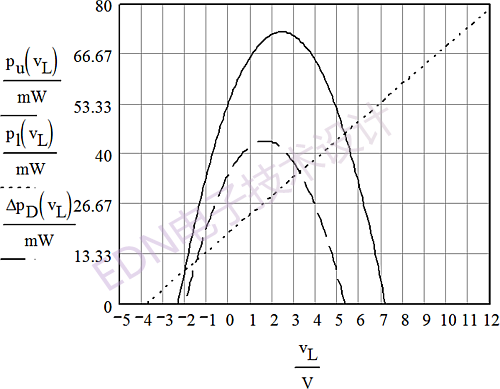

图3是利用MathCAD汇制的功耗图。

图3:利用MathCAD汇制的功耗图。

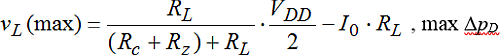

ΔpD最大时,功率随vL的变化最小,这是使热失真最小所需要的。最大差分功率时的vL值为:

另一个感兴趣的电压是pu与pl相等时。在ΔpD = 0W时求解vL:

![]()

在图3中,vL0 = 5.3V。虽然功耗在此输出电压下匹配,但围绕此值的任何变化都会导致ΔpD的变化大于vL(max)附近vL的相同变化。因此,优选的偏置点是vL(max)。

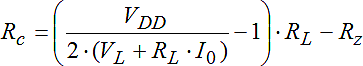

在图3中,vL(max) = 1.62V。但是,给定的电路参数导致静态vL为0V。为了调整JFET上的静态电压,增加了一个额外的串联电阻Rc。一般情况下,让静态输出电压为VL。然后在VL处设置差分功率抛物线的顶点:

![]()

求解满足所需条件的VDD的值:

![]()

然后将VL和供电电压VDD代入下式:

在这个设计中,Rc = 490Ω。Cc绕过Rc,使得漏极处不会出现明显的电压变化。

JFET优于BJT,因为它具有高输入电阻和低输入偏置电流。然而,对于相同的温度系数(TC),JFET的电流匹配必须比BJT好十倍。这就是为什么JFET输入运算放大器的输入失调规范通常比BJT的要差。简而言之,BJT比JFET匹配得更好。

如果您的缓冲设计不需要高输入电阻,请改用BJT。使用QL的固定基极电压,必须以稍微不同的方式实现偏置。这使得QL成为由于VBE(T)而随温度漂移的电流源。发生类似漂移的匹配QU具有相同的偏置电流和动态发射极电阻:

![]()

当ICL(=IEU)随温度变化时,电阻保持恒定。随着温度升高,VBEL降低,ICL升高。同时,reU随热电压VT增加,但增加的发射极电流通过降低reU来补偿。来自QL的电流TC补偿re的变化,这会影响缓冲器电压增益。

这里介绍的基本缓冲级可以通过跟从互补BJT CC级来改进,其中消除了NPN和PNP的b-e结。如果匹配的NPN与QL源串联,它将补偿随后的NPN CC级。

(原文刊登于ASPENCORE旗下网站Planet Analog,参考链接:Buffer Amplifier Design。)

《电子技术设计》2018年9月刊版权所有,禁止转载。

最前沿的电子设计资讯

最前沿的电子设计资讯