在干法刻蚀中,由于与气体分子的碰撞和其他随机热效应,加速离子的轨迹是不均匀且不垂直的(图1)。这会对刻蚀结果有所影响,因为晶圆上任何一点的刻蚀速率将根据大体积腔室可见的立体角和该角度范围内的离子通量而变化。这些不均匀且特征相关的刻蚀速率使半导体工艺设计过程中刻蚀配方的研发愈发复杂。在本文中,我们将论述如何通过在SEMulator3D®中使用可视性刻蚀建模来弥补干法刻蚀这一方面的不足。

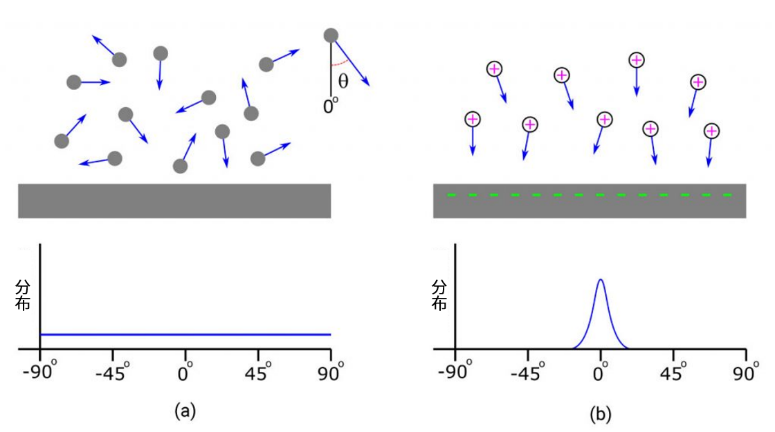

图1a:中性气体在腔室内随机流动的二维展示。气体的行进角度在图中描绘的所有方向上均等分布(图1a)。图1b:显示了带正电的离子和一个带负电的晶圆。离子会因电场而向下加速;然而,由于随机热效应和与其他离子或气体分子的碰撞,完美垂直轨迹无法实现。角速度分布可以近似为高斯函数(图1b)。

角相关刻蚀

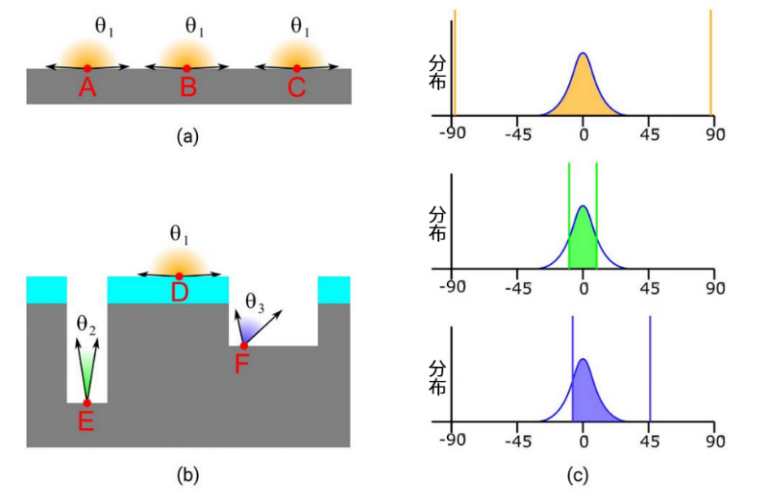

确定材料刻蚀速率(ER)最简单的方法是在实际刻蚀前后测量晶圆的材料厚度。在刻蚀过程中使用平面晶圆可确保局部区域内的所有位置具有相同的张角和离子通量,这将带来可测量的统一刻蚀速率(图2a)。由于不同的刻蚀角度和不断变化的离子通量,在特征相关的刻蚀过程、例如沟槽和硬掩膜刻蚀中,确定该刻蚀速率是不可能的。SEMulator3D能够使用其“多刻蚀”功能模拟此类刻蚀。该软件可测量任意给定点的可见立体角并计算与该立体角范围内离子通量成比例的常态刻蚀量(图2c)。入射角的离子通量分布被假定为具有标准差的高斯分布。

图2a:在平面晶圆表面,每个位置(A、B、C、D)完全暴露在腔室中(开口角为180°),并且接收各个方向的全部离子通量。图2b:在凹坑和沟槽(E、F)底部,腔室视线内的角度范围减小。刻蚀速率可以表示为角度范围内的分布积分(垂直线之间曲线下的阴影区域)。

刻蚀配方剖析

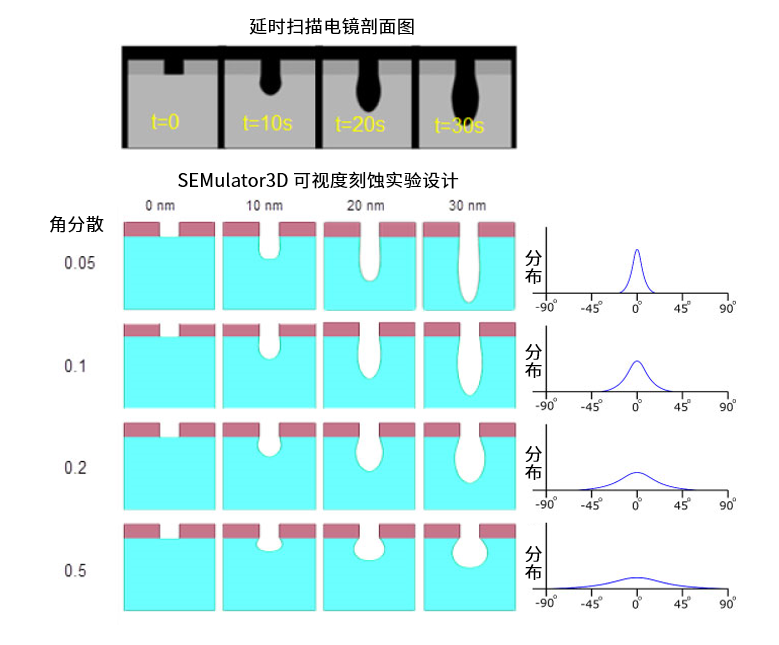

给定刻蚀腔室设置(射频功率和压力设置)的离子角分散可以凭经验用延时刻蚀样品的扫描电镜(SEM)图像确定,随后可以在SEMulator3D中模拟出虚拟腔室内的“虚拟”结构。虚拟实验设计可以在此模型中运行——通过改变角分散,直到虚拟刻蚀建模结果与实际SEM图像轮廓相匹配。图3展示的是,在SEMulator3D中将刻蚀样品的虚拟延时SEM与几个不同厚度的模型进行了比较,显示不同角分散值下的刻蚀形状和深度。SEMulator3D中的厚度设置说明的是在大体积腔室具有完全可视性的区域内理论上最大的材料去除。该设置将与实际刻蚀腔室中样品上的最大离子通量成比例。与实际刻蚀配方最匹配的模拟设置将在每个成比增加的厚度和时间上都具有与SEM图像相匹配的模拟轮廓(3D模拟图像)。开发与相应的实际刻蚀配方相匹配的模拟配方具有重大价值,它可用于预测样品的刻蚀时间演变,并使工艺探索期间在其他应用和结构中使用虚拟刻蚀模型成为可能。

图3:模拟实验设计与延时SEM的比较。模拟实验设计使用了恒定刻蚀量和不同的角分散(高斯分布的标准差),进行模拟并显示增量材料删除步骤失效。右侧的直方图说明了角度分布与软件中数值设置的相关性(不按比例)。刻蚀工艺的实际角分散是通过找到与刻蚀轮廓最匹配的模拟实验设计结果来确定的。

使用剖面配方优化 SADP 样品

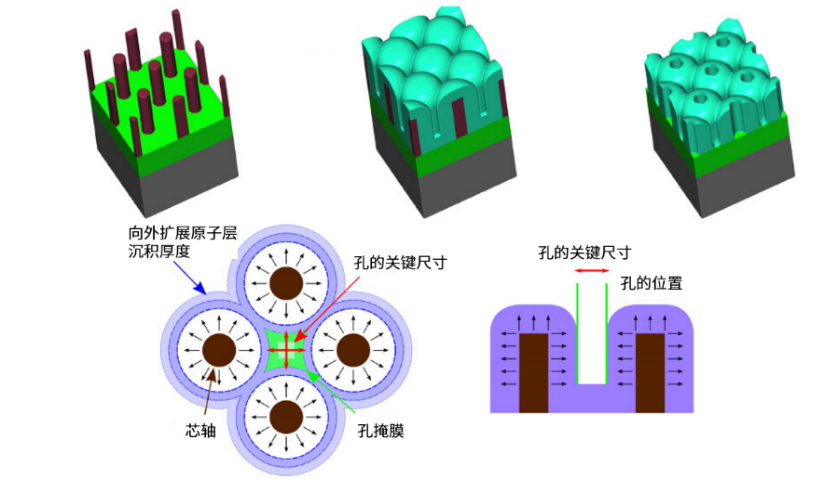

作为SEMulator3D中可视性刻蚀的示例,我们将使用剖面的二氧化硅 (SiO2)和氮化硅 (SiN) 刻蚀工艺模型来确定确保SADP柱孔关键尺寸的均匀性所需的最佳原子层沉积 (ALD) 厚度(见图4)。该样品由50nm SiN层和100nm高的碳芯轴组成,芯轴直径20nm,水平间距80nm。最终目标是使用SADP创建一个40nm间距的孔阵列。此剖面SiN / SiO2刻蚀的角分散为0.08,对所有异物的选择比为0.3。使用ALD形成的孔不对称形状呈现为带有圆形开口的菱形,与在芯轴上形成的圆柱形孔形成对比。由于此菱形孔的大小可以通过ALD进行调整,我们需要确定ALD的临界厚度,刻蚀过程中这一厚度的ALD下进入此菱形孔区域的离子总量与进入圆柱区域的离子总量相等,这将带来相等的刻蚀深度和形状。

图4:孔阵列上的菱形SADP,芯轴直径20nm,水平间距80nm。处于扩张的向外沉积形成了孔,这些孔又形成菱形并具有圆形开口。使用剖面SiO2刻蚀,可以探索不同ALD厚度刻蚀孔的形状。

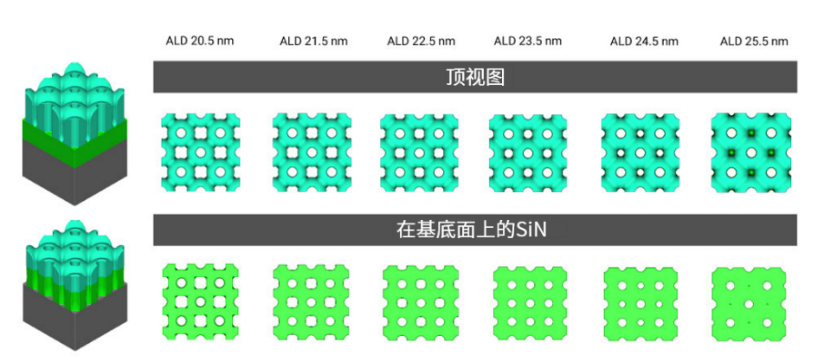

SEMulator3D中可以通过ALD厚度实验设计确定这一最佳厚度。该模拟的结果如图5所示,刻蚀自上而下的形状和底部横截面也可见。随着ALD厚度的增加,SiN /基底界面处的孔形状从方形变为圆形,并且逐渐变小。在足够的ALD厚度下,菱形孔的尖端可视度有限,这会导致较低的刻蚀速率且刻蚀保持圆形。在23.5nm的ALD厚度下得到了此次剖面SiO2和SiN刻蚀工艺最均匀的孔形状。

SEMulator3D中可视刻蚀特征提供了一种模拟与现实刻蚀腔室接近的刻蚀速率的方法。SEMulator3D可视性刻蚀设置,例如角分散和选择比,可以与延时SEM图像进行比较,以验证工艺模型。之后,该工艺模型可以用来探索刻蚀配方变化对不同结构和不同刻蚀次数的影响,免去实际晶圆制造和测试的时间和成本。

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯