从第一次工业革命到现在,人类的科技发展速度一直在加快,我们现在正处于被称为第四次工业革命的时代,其核心正是半导体技术的飞速发展,从日常的吃穿住行,到尖端领域的研发突破,半导体技术的影响渗透入这世界的每一个角落。

大数据和人工智能、超大规模计算、汽车电子、物联网、生命科学、5G技术等作为半导体电子世界的核心推动力,也正推动着整个人类世界飞速向前,作为全球领先的EDA公司,Cadence在这场浪潮中扮演了重要角色。在IIC Shanghai 2024国际集成电路展览会暨研讨会同期举办的“2024中国IC领袖峰会”上,Cadence数字产品资深高级总监刘淼进行了“当汽车电子遇见3D-IC”的主题演讲,分享了Cadence在汽车电子与3D-IC发展方面的独到见解。

Cadence数字产品资深高级总监刘淼

在汽车电子领域,Cadence强调了三个关键要素:安全、可靠和质量。对此,刘淼表示Cadence正与车规芯片行业内的领先企业如TI、NXP、Renesas、ADI、ST、BOSCH等合作,持续推动汽车电子行业的发展。同时,Cadence也支持中国企业以及新势力,如特斯拉、小鹏、未来和CRUISE等,帮助他们通过芯片设计构建自己的竞争优势。

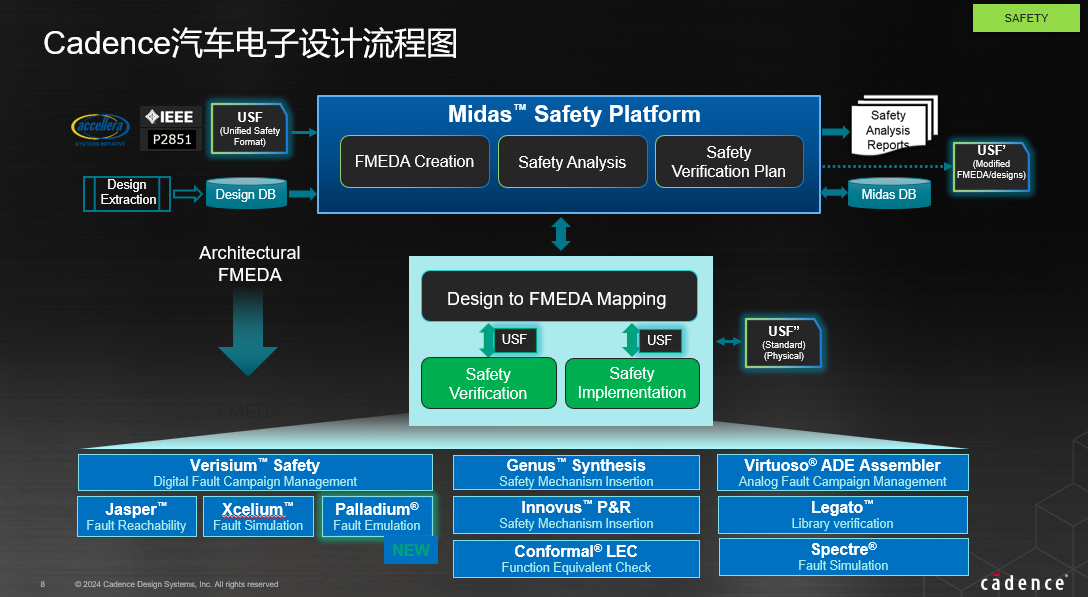

在演讲中,刘淼展示了Cadence的汽车电子设计流程图,安全标准格式(USF)是其核心。安全工程师可以利用USF进入MEDAS平台,完成FMEDA的建立、验证计划以及安全分析。同时,基于USF,还可以进入仿真或实现平台,去完成安全验证或安全实现。Cadence的USF包含着很多工具,如Genus、Innovus、Conformal等,都天然的支持这一格式。

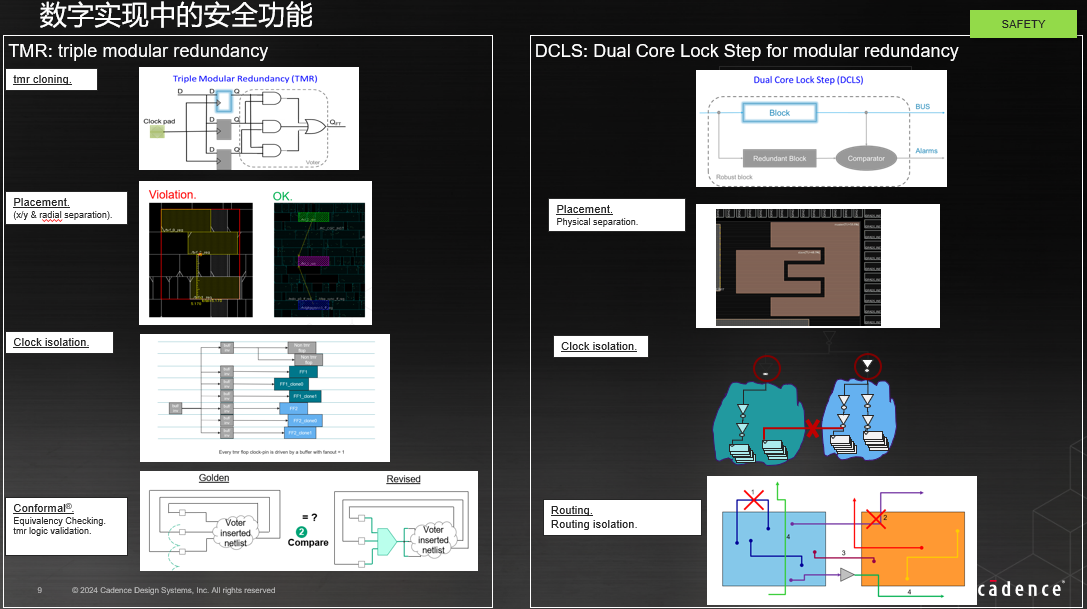

为了更直观地显示数字实现中的安全功能,刘淼还介绍了TMR和DCLS安全岛机制作为案例:

刘淼表示:“Cadence车规数字设计流程很简单,什么叫EDA?就是能够让工程师提升效率的工具,它是一个自动化的东西,所以我们在汽车电子和普通的芯片设计上面对用户来说改变很小,比如通过Midas产生了USF,USF成为Genus的一部分,它可以读进去,工具就会自动去做比如说TMR的嵌入或者是逻辑上面的综合预防。在Innovus实现工具上面,当你读入了USF以后,工具自动会做判断,自动去做DCLS的生成,自动去避免时钟、嵌入方面的问题。”

根据介绍,Cadence的自动化工具不但可以自动进行布局和布线、自动生成任意边界的DCLS隔离,还可以进行自动校核检查,如其最新的Voltus Insight工具,基于机器学习和深度学习算法,可以发现和修复IR问题,确保芯片的性能。面对汽车芯片庞大的面积,Cadence工具的高度自动化,可以大大减少工程师的工作量,提高开发效率。

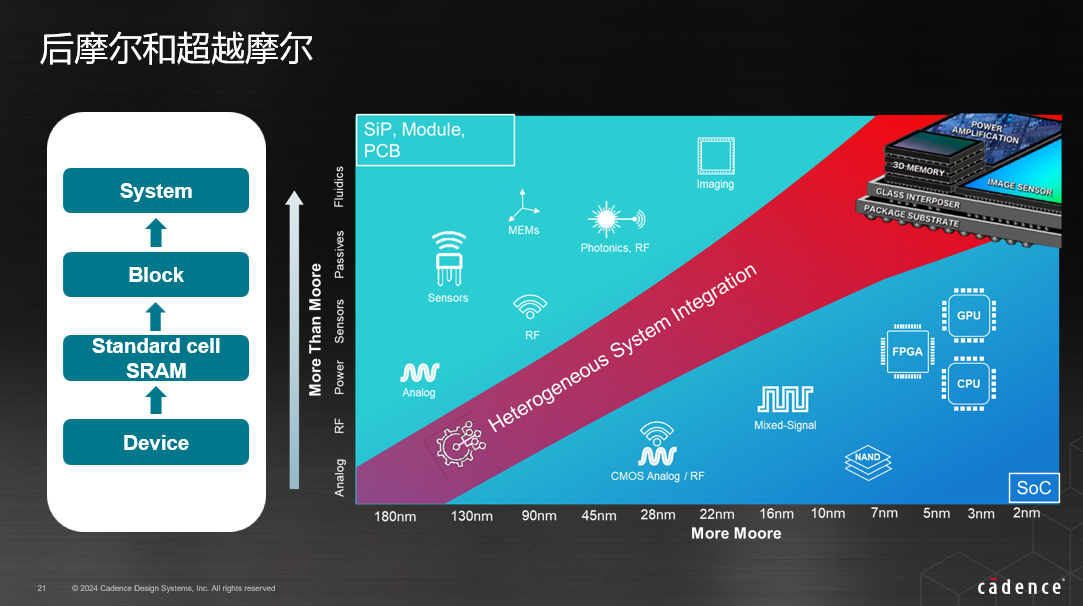

在汽车电子和高级驾驶辅助系统(ADAS)芯片的发展中,Cadence公司正处于技术革新的前沿。随着自动驾驶技术的不断进步,对芯片的要求也越来越高,这不仅体现在算力上,还体现在功耗和互连能力上,Cadence通过引入对3D-IC技术的支持,以应对不断升级的挑战。

Cadence所引入的3D-IC技术是对传统2D芯片的一次重大突破,3D技术所带来的是指数级的连接密度的提升,将极大的提高芯片性能和减少功耗。刘淼举了一个最为直观的案例,2.5D技术的HBM总线长为107um,使用3D技术可以将HBM总线长缩短至2×105um,缩减近两个数量级。

刘淼指出:“从3D-SIP到2.5D一直到3D,中间有一个重要的指标就是它的pitch间距,从500微米减到50,然后到20,到7,到1,甚至进入纳米级别。这些Pitch带来2次方、4次方、6次方的连接密度提升。”

目前,Cadence支持封装级和晶圆级的3D-IC设计,包括同构和异构设计,提供了一系列工具和服务来支持3D-IC的设计和实现。例如,Cadence通过其Integrity 3D-IC工具,提供了一个统一的数据库来分析和优化芯片的功耗。此外,Cadence还开发了3D mixed placer技术,可以同步优化多个die的布局,以支持更复杂的3D-IC设计。

Cadence在3D-IC领域的深入研究与探索,为汽车电子和ADAS芯片的未来发展奠定了坚实的基础。今后,Cadence将继续积极与世界各地的优秀厂商进行合作,在全球范围内加速创新和发展,共同推动3D-IC技术不断向前。

最前沿的电子设计资讯

最前沿的电子设计资讯