前言

近年来有关第三代半导体的市场题材相当多,其中最令人瞩目者,当属碳化硅(SiC)功率器件在电动汽车的应用商机了。碳化硅器件在电动汽车的系统应用主要是逆变器、车载充电器(OBC)和DC-DC转换器等。相较传统的硅基模块性能,其可减少约50%电能转换损耗、降低20%的电源转换系统成本,并能提升电动汽车4%左右续航能力。UlOednc

目前电动汽车技术在世界各国净零碳排放政策强力带动下,已成为未来10年全球汽车产业的发展重点,许多大厂争相投入此领域布局。例如鸿海集团在2021年斥资37亿元进驻新竹科学园区,藉由并购旺宏6英寸厂成立全资子公司“鸿扬半导体”,以作为其碳化硅研发中心,打造完整的电动汽车供应链。另外,继2018年特斯拉率先把碳化硅器件集成到Model 3量产车款内,包括通用汽车(GM)和大众汽车等,也都已宣布将在2022年新车款引入碳化硅相关技术。而意法半导体(ST)与雷诺日产三菱联盟及比亚迪也已达成战略合作协议,长期为其车载充电器提供碳化硅器件。雷诺日产三菱联盟预定于2030年前推出多达30款电动汽车,投资金额将超过200亿欧元,藉以抢进在电动汽车领域的市占率。由近期市场动态可以清楚预见,碳化硅功率器件将快速成为车用半导体产业的明日之星。UlOednc

本刊这期特别通过台湾闳康科技邀请了在第三类半导体研究领域顶尖学者崔秉钺教授,为本刊撰文介绍碳化硅功率器件的发展概况与技术趋势,与读者分享此一重要科技领域的学术研究进展。UlOednc

高温与高击穿电压耐受能力——碳化硅的绝佳优势

功率半导体器件广泛应用于电力系统、电源供应器、汽车电子、电机控制、无线射频系统、通信设备或薄膜晶体管液晶显示器等方面。由于Si价格低廉且技术成熟,目前绝大多数的功率半导体器件均为Si器件。然而,因为Si的禁带宽度只有1.12eV,在大功率应用时,有一些基本限制,包括低击穿电压、高特征导通电阻(Ron,sp)、大反向偏置漏电流、低工作温度等。也因为耐压以及导通电阻的限制,在大功率应用时,必须使用双载流子器件——例如PiN二极管(PND)或绝缘栅双极型晶体管(IGBT)——取代单载流子器件——如肖特基势垒二极管(SBD)和金属氧化物半导体场效应晶体管(MOSFET)——这也使得功率与速度无法兼顾。基于以上因素,碳化硅(SiC)、氮化镓(GaN)等宽禁带半导体材料在近十年备受瞩目。UlOednc

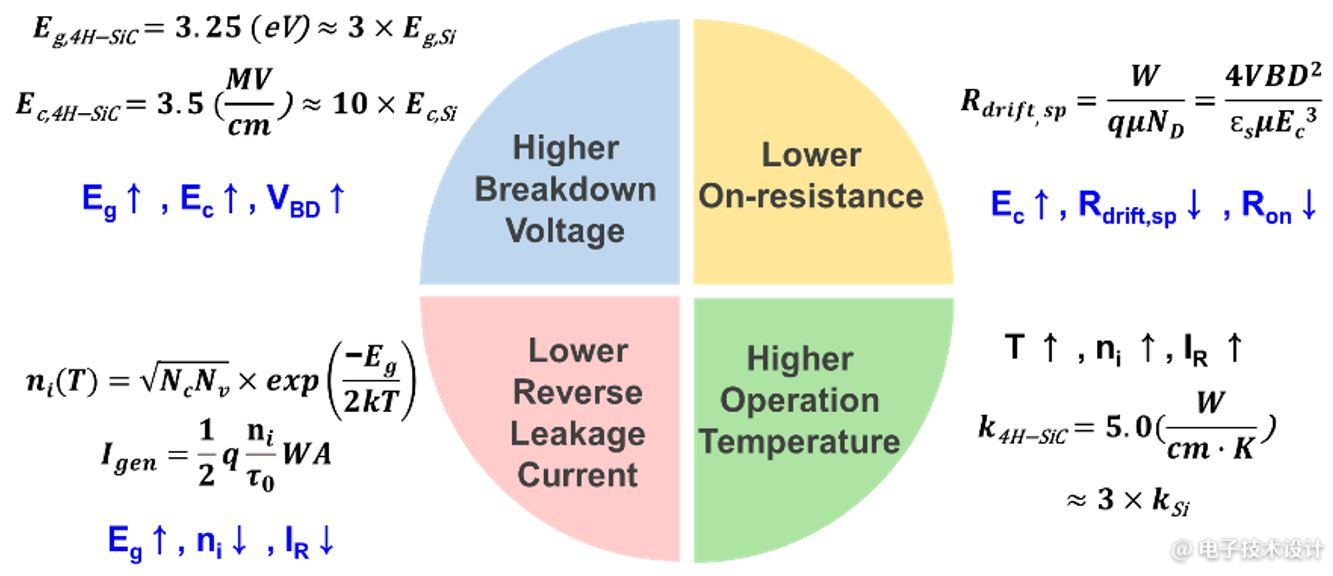

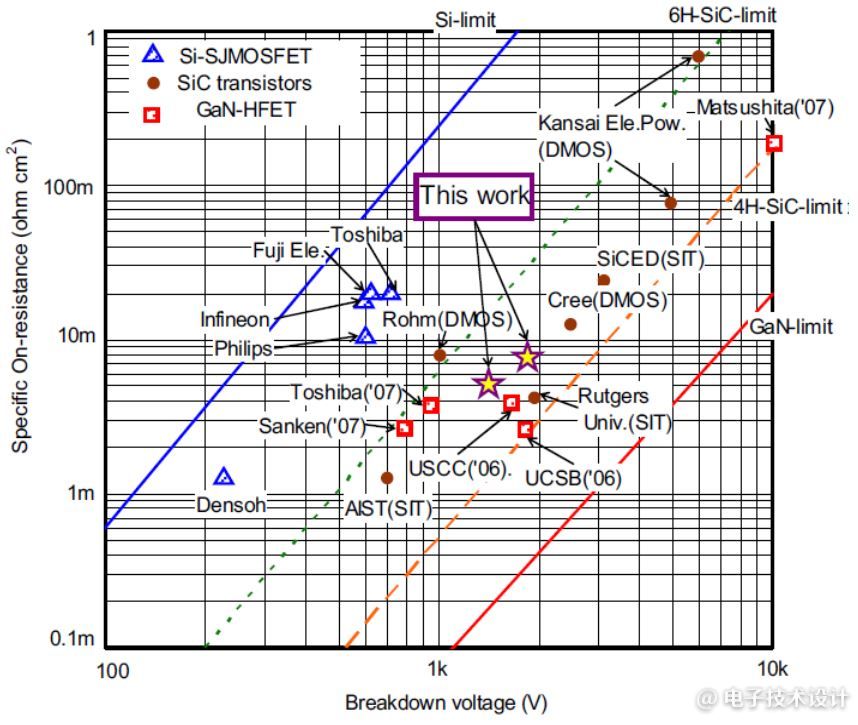

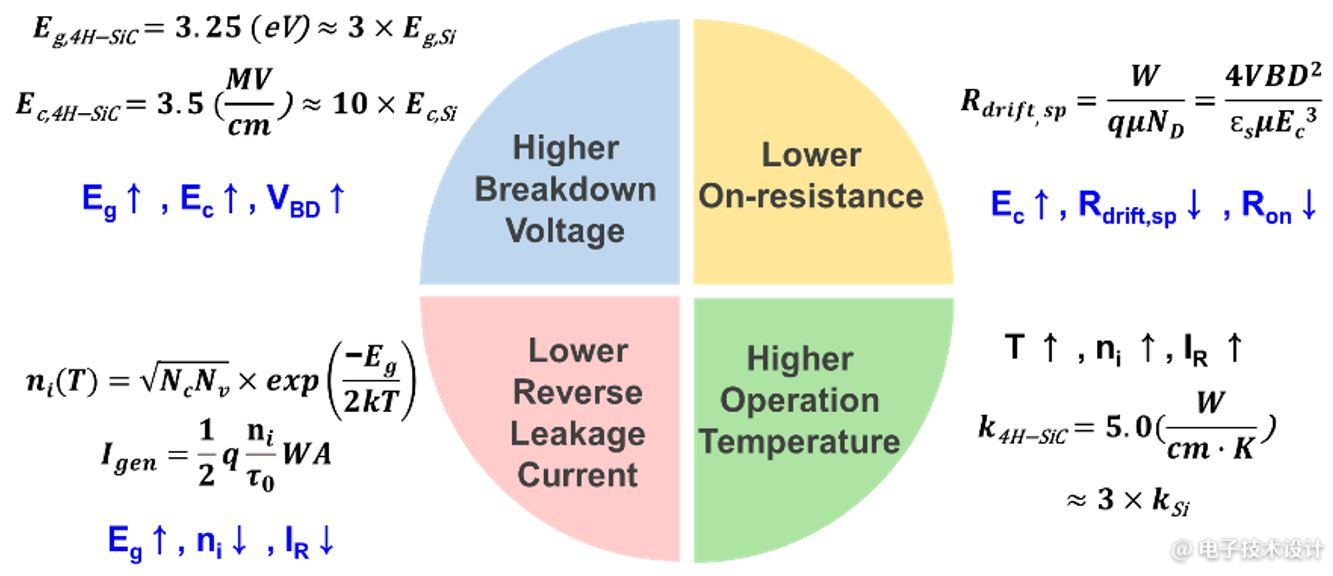

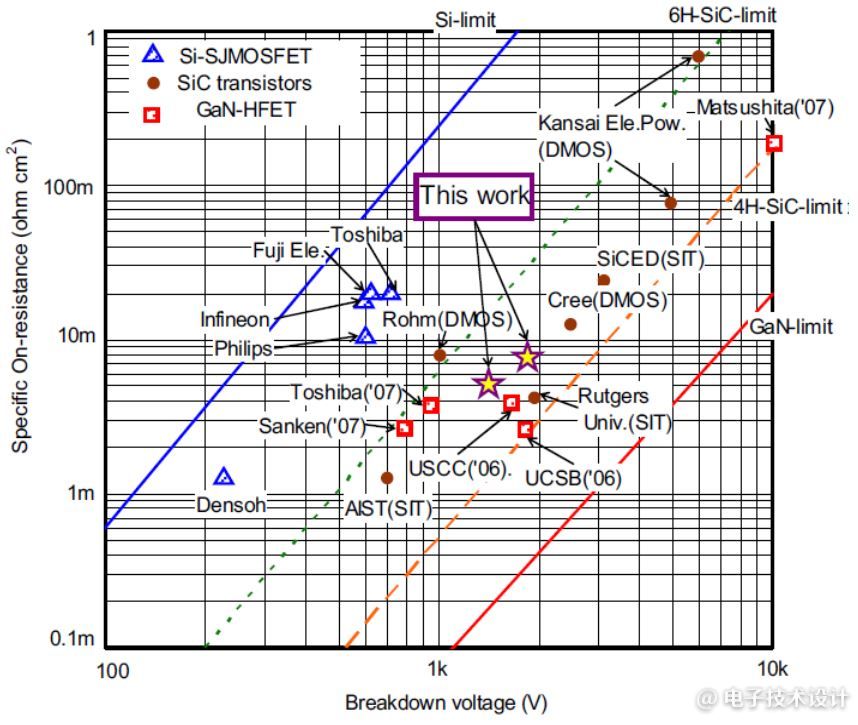

SiC有250种结晶形态,其中的4H-SiC已经确定是最适合制作大功率半导体器件的结晶相。4H-SiC的禁带宽度是3.25eV,即使在300℃,本征载流子浓度仍低于室温下的Si,所以很适合在高温环境操作;4H-SiC的临界击穿电场比Si高10倍,可以在高10倍的掺杂浓度下,达到10倍的击穿电压,因为掺杂浓度提高、载流子漂移区缩短、特征导通阻抗可以降低100倍以上(图1)。GaN的载流子迁移率比4H-SiC高,可望有更高的工作频率以及更低的导通阻抗,而4H-SiC的导热系数比GaN大三倍,适用于大功率且高温的环境。UlOednc

UlOednc

UlOednc

图1:SiC的材料和物理特性,以及这些特性在大功率系统的应用优势[1]。UlOednc

碳化硅功率器件的应用

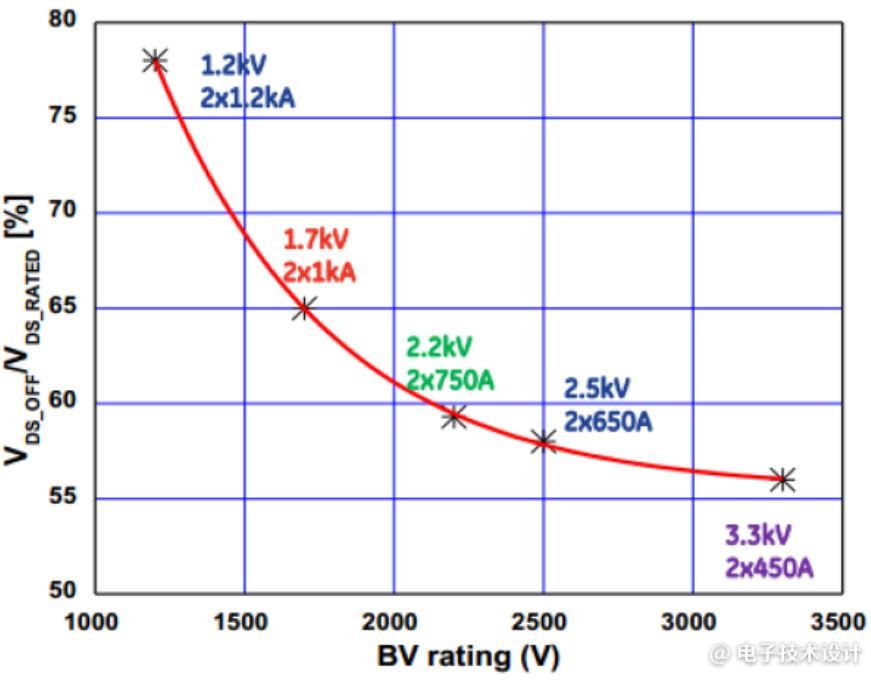

大功率器件在应用时,功率器件的额定电压必须大于系统电压。以电动汽车为例,目前主要的电动汽车电池电压是400V,但是考虑到功率模块的可靠度后,实际使用650V等级的功率器件。UlOednc

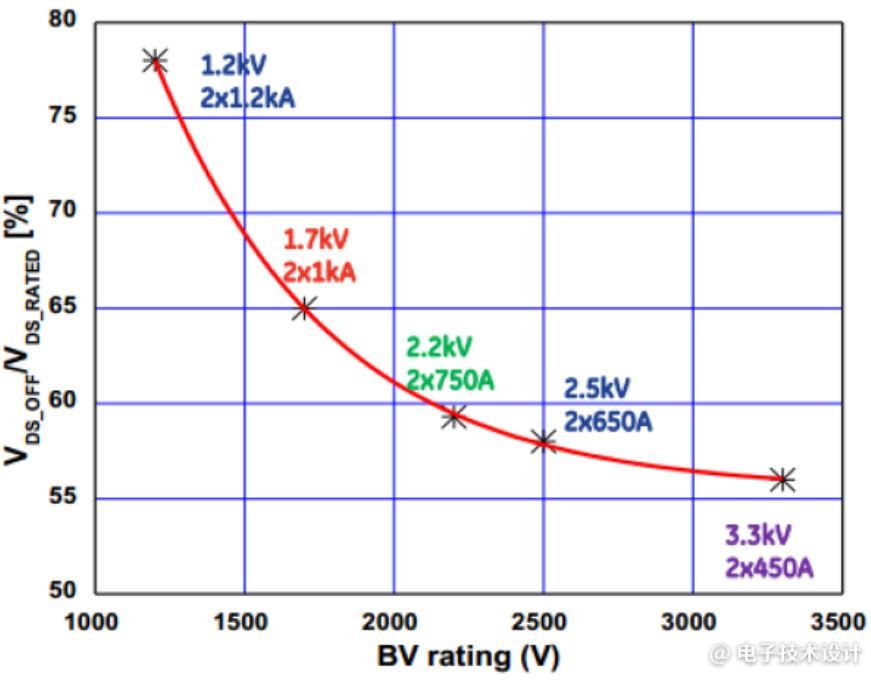

图2显示了FIT=100的系统电压和额定电压的比例[2],系统电压愈高,系统电压和额定电压的比例愈低,表示需要更高击穿电压的功率器件。当电动汽车电池电压提高到800V时,需要使用1.2kV等级的功率器件。UlOednc

UlOednc

UlOednc

图2:故障率FIT=100的应用电压和额定电压的比例[2]。UlOednc

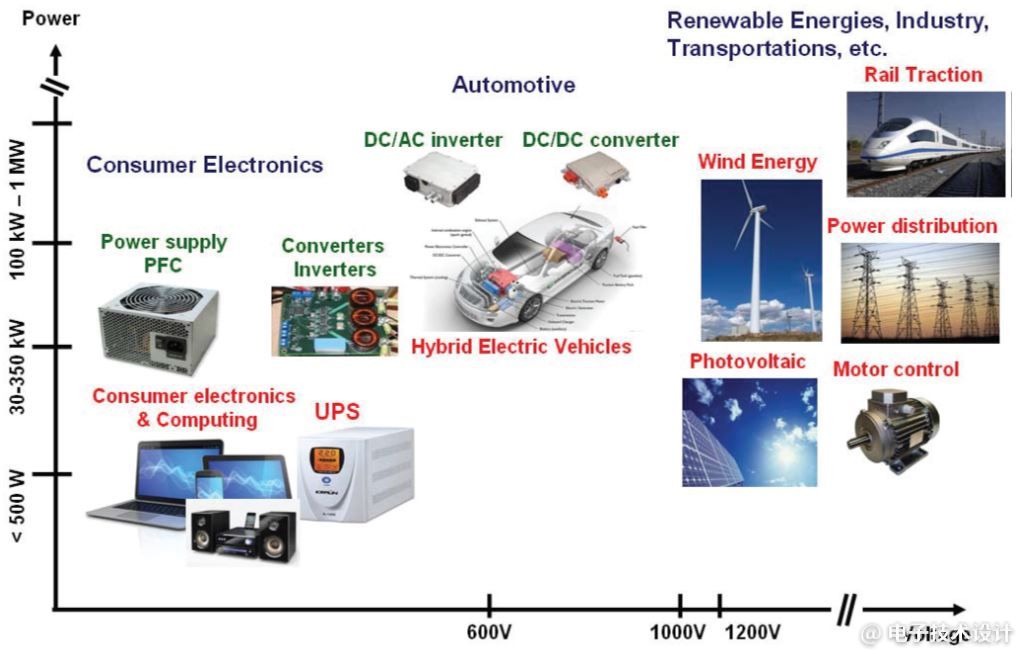

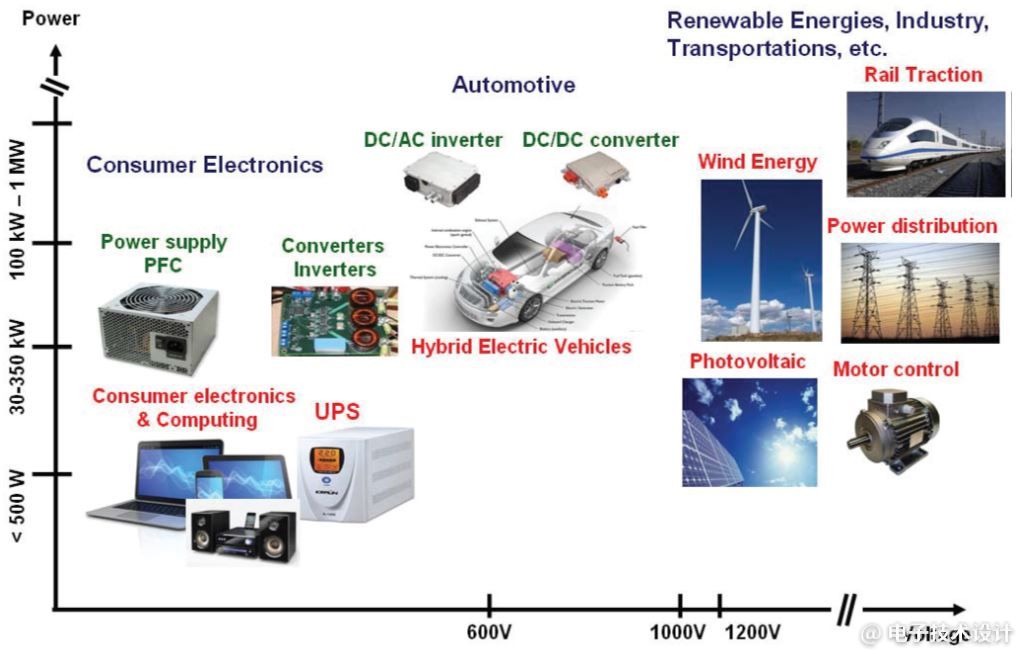

时至今日,欧美日等SiC器件大厂,例如ST、Infineon、Wolfspeed、Rohm等公司均有成熟的650V、1.2kV等级的SiC MOSFET产品,广泛应用于电动汽车和充电设施。更高电压的应用或更恶劣的应用环境需要使用更高等级的功率器件,例如风力发电机的电压虽然低于1kV,但是需要使用1.7kV等级的功率器件;太阳能发电趋势会提高到1.5kV,届时将需要3.3kV的功率器件。其他应用,如轨道运输、高速铁路、智慧电网、工业电机等,也都会需要3.3kV甚至更高额定电压的功率器件,如图3所示[3],日本的新干线最新的N700列车就是采用3.3kV的SBD。UlOednc

UlOednc

UlOednc

图3:SiC大功率器件的应用领域[3]。UlOednc

肖特基势垒二极管(SBD)

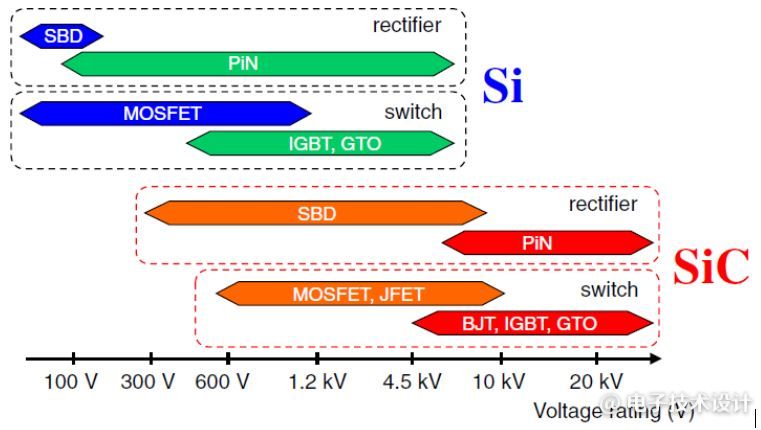

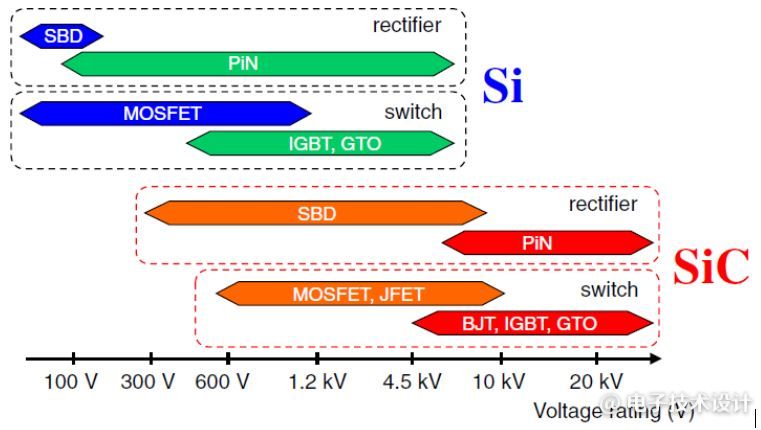

分立式的功率器件,基本上分成整流用途的二极管以及开关用途的晶体管,因为要导通大电流,故以垂直结构为主。SiC功率器件发展的轨迹基本上是跟随Si功率器件,最先进入量产的是SBD类型的二极管,根据细部结构的不同,有肖特基势垒二极管(SBD)、结势垒肖特基二极管(JBSD)、沟槽结势垒肖特基二极管(TJBS)等,其结构示意图如图4所示,虽然还有微调优化的空间,但已是成熟的器件。因为SiC的SBD击穿电压可以涵盖Si的PND,既然SBD的速度高于PND,SiC的PND要在更高压的应用上才需要使用,Si和SiC功率器件的种类和适用的电压范围如图5所示[4]。UlOednc

UlOednc

UlOednc

图4:SBD类型二极管的结构示意图。UlOednc

UlOednc

UlOednc

图5:Si和SiC功率器件的种类和适用的电压范围[4]。UlOednc

金属氧化物半导体场效应晶体管(MOSFET)

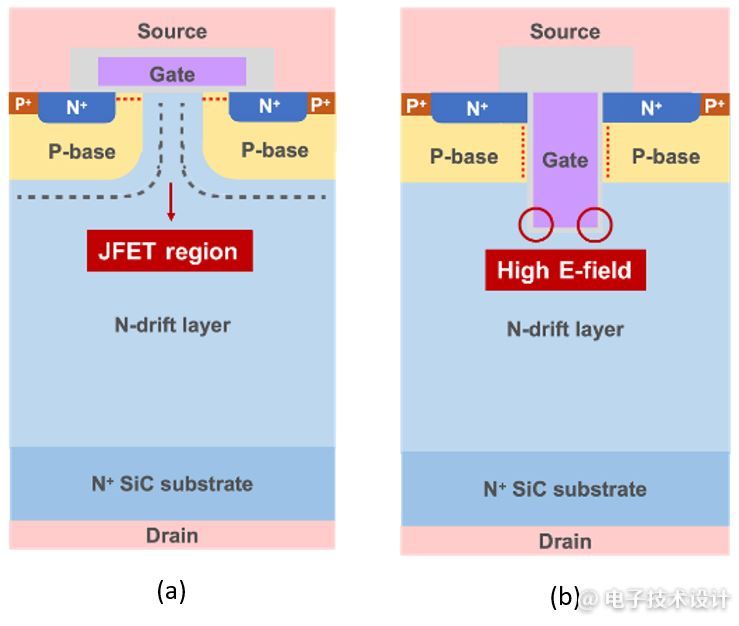

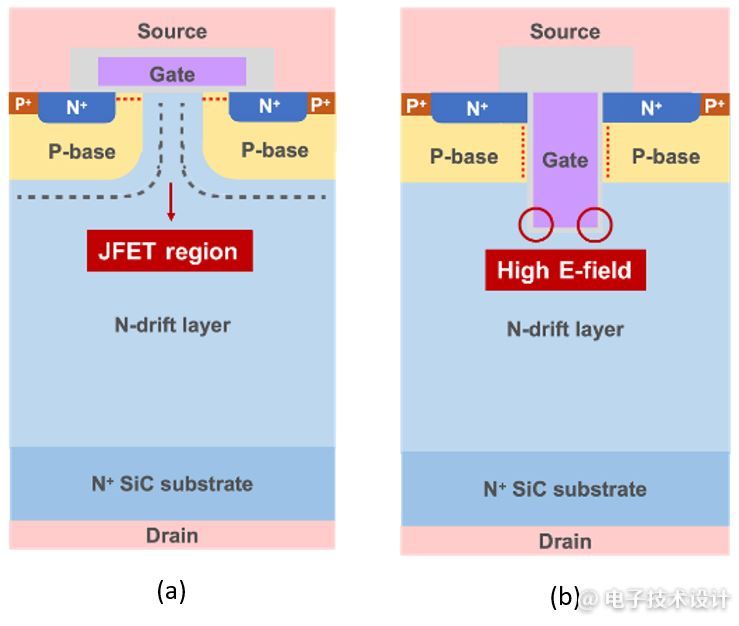

大功率MOSFET有两种结构,第一种是平面通道的垂直双注入金属氧化物半导体场效应晶体管(VDMOSFET),其剖面结构如图6(a)所示;第二种是垂直通道的沟槽栅极或称U形栅极金氧半场效应晶体管(UMOSFET),其剖面结构如图6(b)所示。VDMOSFET的优点是工艺比较简单,因为工艺造成的可靠度问题比较单纯。最关键的工艺是栅极氧化,要有适当的SiO2/SiC接口钝化,以提高载流子移动率,降低沟道电阻对特征导通电阻影响,同时要有足够的可靠度。目前以NO或是N2O退火的氮钝化效果最好,但是电子迁移率只能达到30~50cm2/V-sec左右,和块材中的1000cm2/V-sec相去甚远,如何提高载流子迁移率到100cm2/V-sec以上,是各大厂商以及学术机构努力的方向。UlOednc

UlOednc

UlOednc

图6:(a)垂直型大功率VDMOSFET的剖面图、(b)沟槽栅极UMOSFET的剖面图。UlOednc

平面沟道的结构使得单元间距不容易缩小,相邻的p型基体(P-body或P-base)造成的结型场效应晶体管(JFET)效应也会增加导通电阻。UMOSFET的单元间距在相同的工艺水平下,大约是VDMOSFET的60%,而且理想上可以消除JFET效应,得到较低的导通电阻。UlOednc

但是UMOSFET的工艺比VDMOSFET困难,沟槽蚀刻工艺以及沟槽侧壁的栅极氧化工艺,都需要精准控制。特别是为了降低沟槽底部的电场,需要增加很多工艺步骤,例如Rohm采用双沟槽结构,如图7(a)所示[5];Infineon采用不对称的沟槽结构,如图7(b)所示[6];或是在沟槽底部增加P+屏蔽层,如图7(c)所示[7]。然而这些做法除了增加工艺成本,也会产生JFET效应。UlOednc

UlOednc

UlOednc

图7:(a) Rohm提出的Double trench UMOSFET[5]、(b) Infineon提出的不对称UMOSFET[6]、(c) Mitsubishi提出在沟底部增加P+屏蔽层的UMOSFET[7]。UlOednc

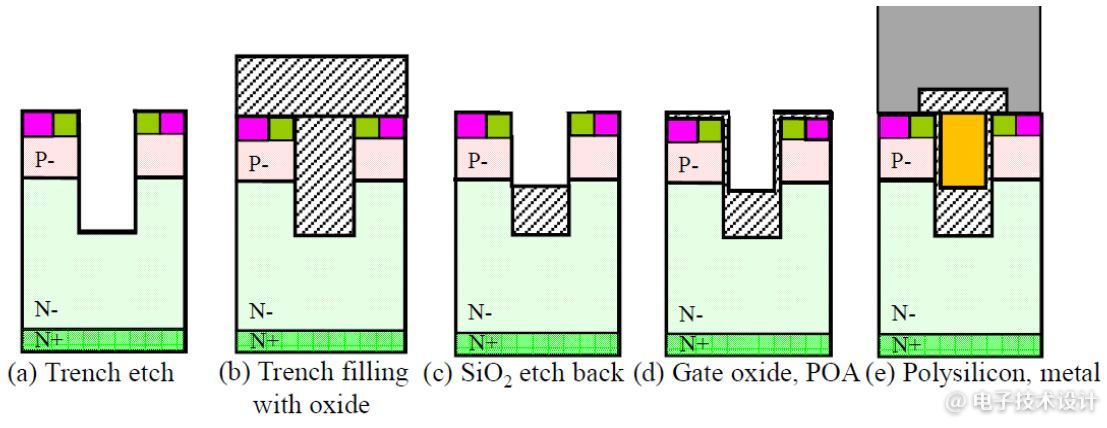

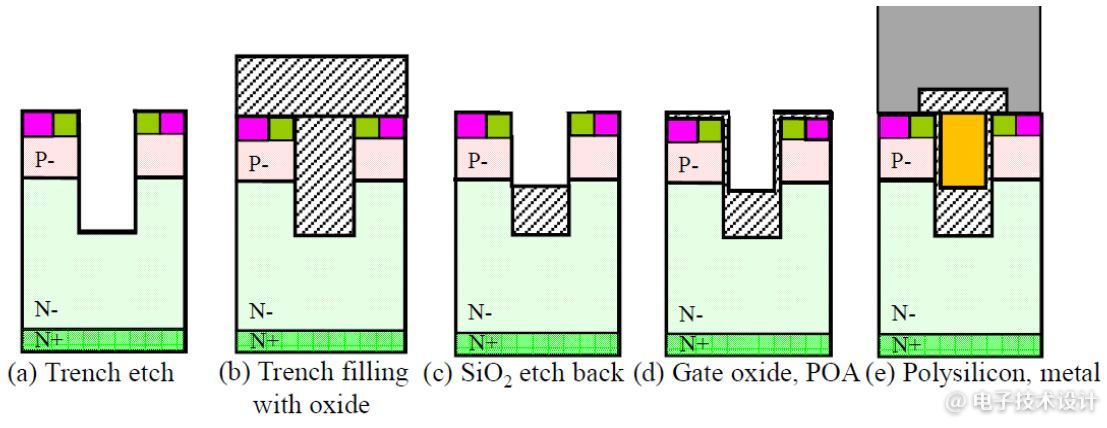

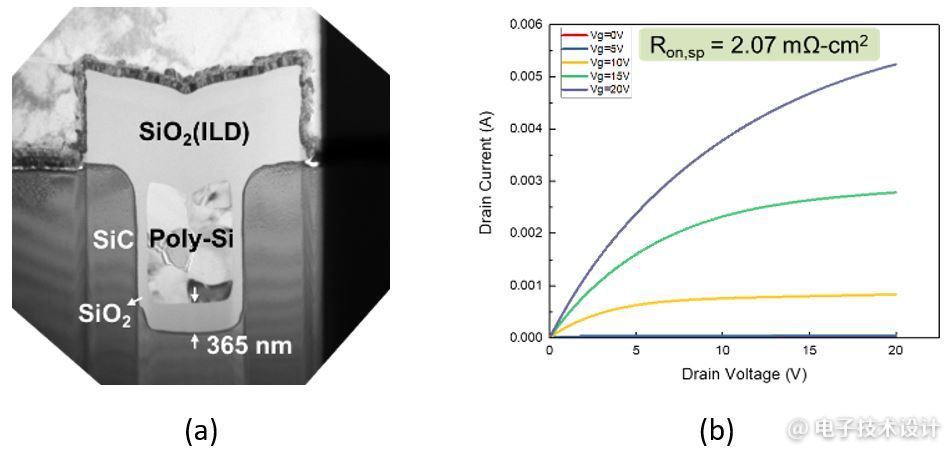

另一种避免沟槽底部栅极氧化层电场过强的方法是增加沟槽底部的氧化层厚度。增加沟槽底部栅极氧化层厚度的SiC UMOSFET论文,迟至2013年才由Toyota公司的Takaya团队发表[8],最大电场强度降低46%,Qgd降低38%,导通电阻仅微微增加4%,如图8所示。但是因为需要在沟槽中填满SiO2,再以回蚀方式保留沟槽底部的SiO2,此TBOX氧化层的厚度变异使得器件特性变异偏大,在没有更好的工艺技术之前,TBOX结构仅止于研究,不适合量产。UlOednc

UlOednc

UlOednc

图8:Toyota提出的增加沟槽底部栅极氧化层厚度的TBOX UMOSFET工艺[8]。UlOednc

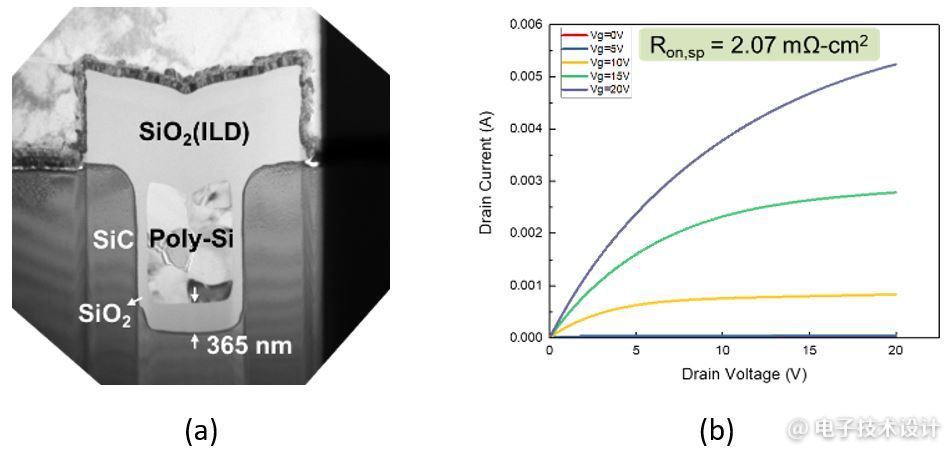

台湾阳明交大电子所崔秉钺教授实验室曾提出利用氩离子植入非晶化(Ar-PAI)工艺提高沟槽底部氧化速率来形成TBOX的研究计划,成功制作出TBOX结构,如图9(a)所示。虽然尚未完成完整的功率器件制作,但是对1.2kV等级的UMOSFET,曾经在单一沟槽测试结构测得2.07m-cm2的Ron,sp,如图9(b)所示,显示此Ar-PAI TBOX UMOSFET的潜力。UlOednc

UlOednc

UlOednc

图9:(a)子计划一、三主持人提出的TBOX UMOSFET实作结构、(b)单一沟槽TBOX UMOSFET的导通特性。UlOednc

因为结构和工艺复杂,UMOSFET的可靠度问题比VDMOSFET严重,因此,虽然UMOSFET已经出现在Wolfspeed和ST公司网站公布的技术蓝图上,目前仍只有Rohm、Infineon、Bosch、Mitsubishi四家公司推出UMOSFET产品,其它如Wolfspeed、ST等十余家公司的产品都是VDMOSFET。UlOednc

超结结构

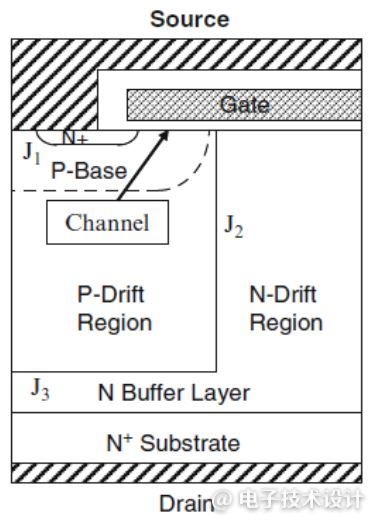

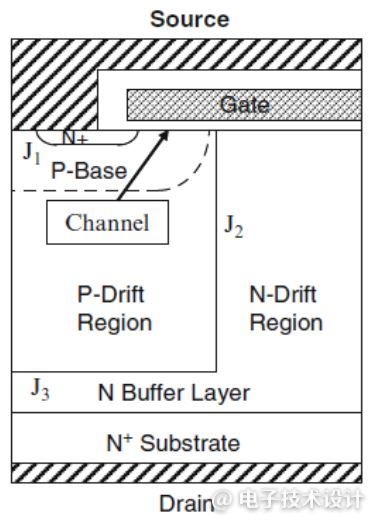

功率MOSFET为了承受高电压,漏极端会有一个低浓度的漂移区,漂移区的电阻正比于击穿电压的2.5次方,也就是说,随着电压的增加,导通电阻会急速增加,造成严重的导通功率损失。图10显示了漂移区的特征导通电阻与击穿电压的关系,这是传统功率器件的理论极限。如果要突破此极限,唯一的方法是采用超结(SJ)结构[9],其结构如图11所示[10],跟传统大功率MOSFET结构的主要差异在漂移区中加入P型柱或P型掺杂区(P-Drift Region)。在逆向偏压时,P型柱和N型漂移区之间的结使得整个漂移区耗尽,因此可以用比较薄的漂移区;此外,因为有P型柱帮助N型漂移区达到耗尽,所以N型漂移区的浓度可以比传统漂移区高。这两个因素造成顺向导通时的SJ漂移区的导通电阻降低。UlOednc

UlOednc

UlOednc

图10:Si、SiC、GaN三种半导体材料的导通阻抗和击穿电压的理论极限[7]。UlOednc

UlOednc

UlOednc

图11:SJ MOSFET的剖面结构示意图[9]。UlOednc

SJ结构是制作在漂移区,所以可以搭配VDMOSFET或是UMOSFET,当然也可以搭配SBD类型的功率器件。但是SJ结构的制作对SiC来说相当困难,因为绝大多数掺杂元素在SiC中都不会扩散,要形成P型柱的方法之一是先蚀刻去除该区域的N型漂移区,再外延P型柱,但是SiC外延难度远高于Si,就笔者所知,尚无成功从沟槽中外延的文献发表。另一种制作P型柱的方法是多次外延搭配多次离子注入。虽然AIST在2021年的ISPSD研讨会率先发表了3.3kV的SJ MOSFET,但是动用了16或是28次外延与离子注入,恐非量产可以接受的工艺[11],需要简化制作方式才有商业化的机会。UlOednc

碳化硅集成电路发展演进

控制MOSFET开关需要栅极驱动电路,目前SiC MOSFET的驱动电路均以Si IC制作,虽然SiC功率器件可以承受比Si功率器件更严苛的环境,但是Si IC不然,因此必须独立封装、隔离,增加了功率系统的体积;信号传递时受封装导线的电感与电容影响,增加功率损耗、影响性能,最理想的情况还是以SiC IC驱动,才能够完整发挥SiC的材料优势。因此,能与垂直MOSFET集成的SiC IC技术,也是近年愈来愈受到重视的研究主题。UlOednc

- SiC IC的研究始于20世纪90年代初期,当时采用的是6H-SiC,陆续实现了数字和模拟电路区块[12-15]。

- 1994年美国普渡大学发表了第一个NMOSFET电路,展示逆变器、NAND、NOR、XNOR、D锁存器、RS触发器、二进制计数器和半加器等基本电路单元[12]。

- 1999年普渡大学和康乃尔大学共同发表了第一个以6H-SiC制作的智能栅极驱动电路,包含了过压、低压、短路、开路的检测功能,并可以在300℃的环境下工作[16]。随后,因为载流子迁移率较高的4H-SiC晶体成长技术成熟,相关研究转向使用4H-SiC。

- 2006年Cree公司发表第一个4H-SiC CMOS逆变器[17]。

- 在2011-2013年间,英国雷神公司(RSL)陆续发表了4H-SiC CMOS IC工艺以及基本逻辑单元[18-20],此高温碳化硅工艺简称为HiTSiC工艺。

- HiTSiC工艺推出后,2016年美国阿肯色大学发表了SiC MAC、NCL计数器、布尔FSM和DAC控制器等电路[21]。

- 2017年英国的纽卡斯尔大学展示了混合信号IC应用,例如555定时器以及4:1多路复用器[22];最近阿肯色大学发表了更复杂的数字控制的PWM发生器电路[23]。同年,日立公司发表了SiC CMOS运算放大器[24],采用最基本的MOSFET结构,展示SiC CMOS抗辐射的能力。

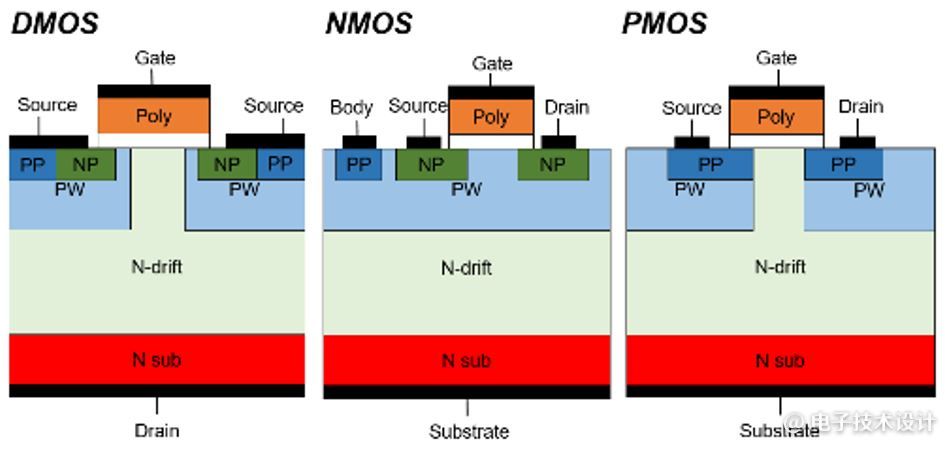

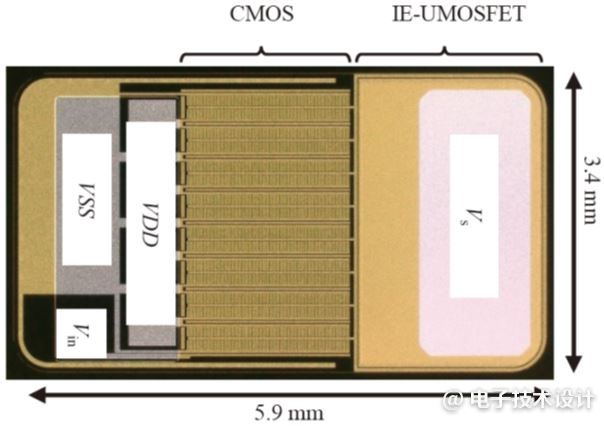

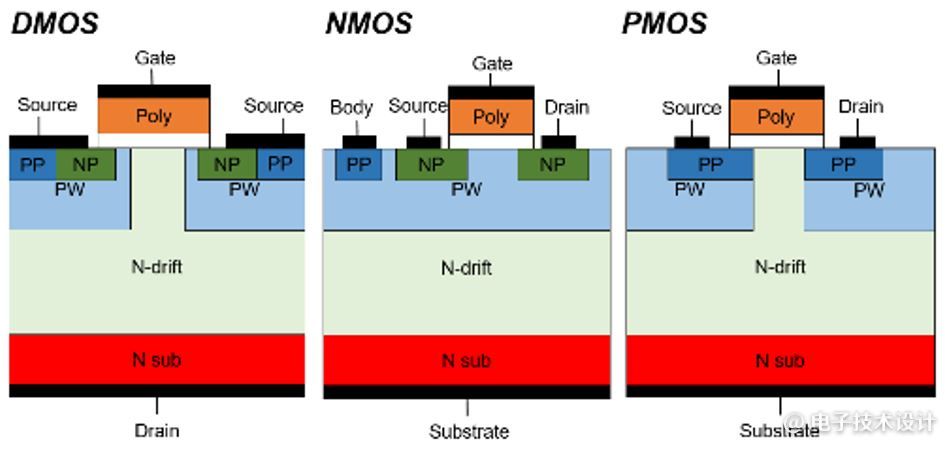

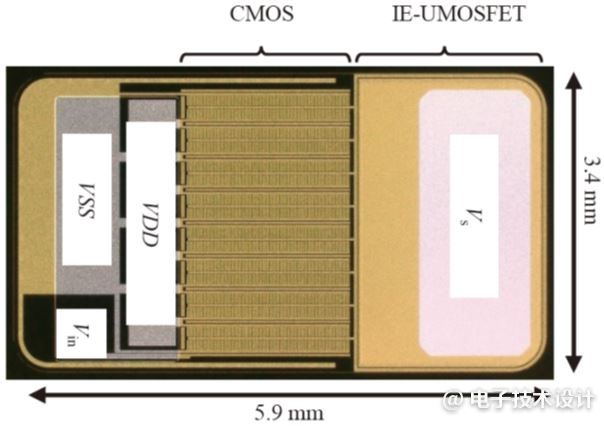

- 2021年1月,台湾清华大学黄智方教授(半导体射月计划成果)在“IEEE Electron Device Letters”率先发表了800V的横向LDMOSFET和低压CMOS的单芯片集成,如图12所示[25]。日本的AIST则在同年的ISPSD研讨会发表了单芯片集成1200V等级的沟槽式栅极MOSFET以及CMOS栅极驱动电路的成果,是首度集成低压CMOS和垂直式的功率器件,如图13所示[26]。

UlOednc

UlOednc

图12:台湾清华大学黄智方教授团队(半导体射月计划成果)在IEEE EDL发表了800V的横向MOSFET和CMOS集成[26]。UlOednc

UlOednc

UlOednc

图13:AIST在2021年的ISPSD研讨会发表的集成1200V等级的沟槽式栅极MOSFET以及CMOS栅极驱动电路的单芯片[24]。UlOednc

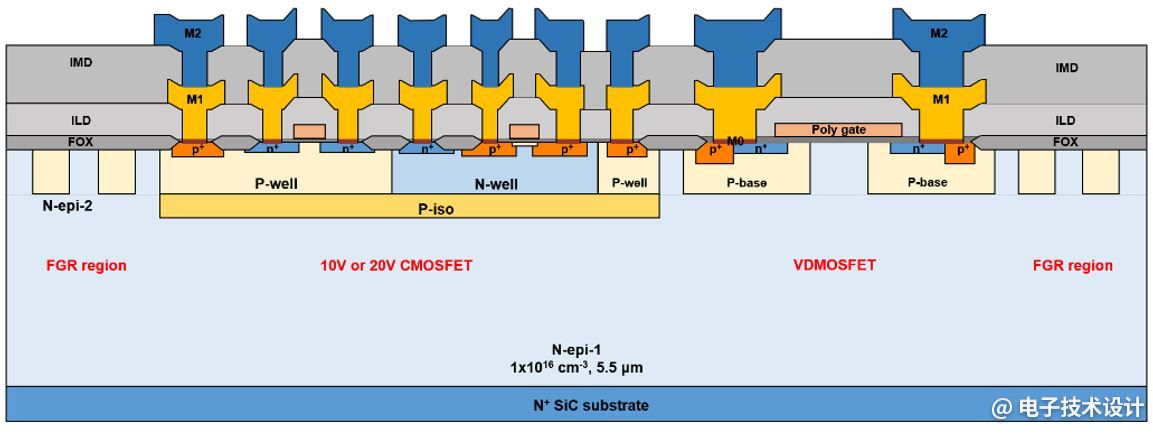

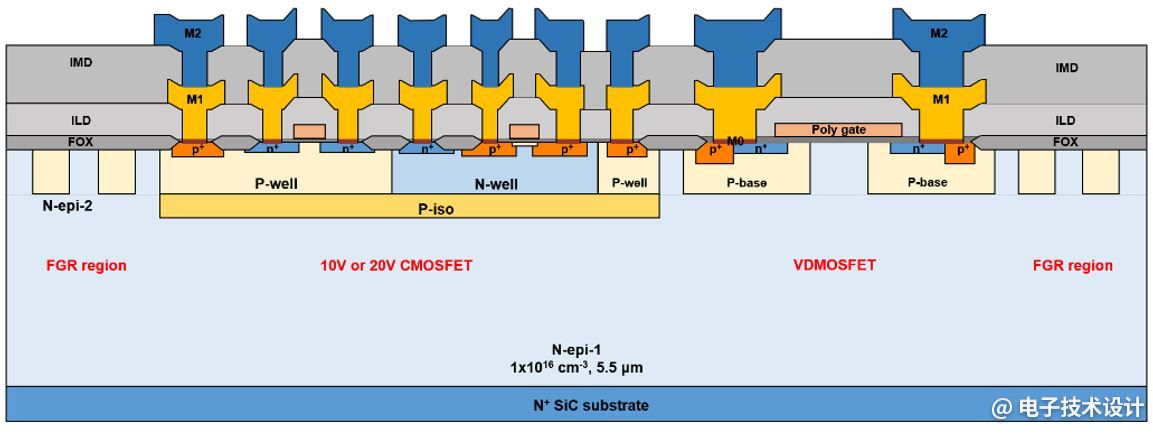

本实验室在半导体射月计划的支持下,开发出局部氧化隔离工艺、双栅极氧化层厚度工艺、P型多晶硅栅极工艺、高低压器件结隔离工艺等关键技术,成功地在2021年完成10V CMOS+20V栅极驱动器+60V VDMOSFET单芯片集成,成果将发表于2022年的VLSI-TSA以及ISPSD研讨会[27, 28],图14是剖面结构示意图。而在ISPSD之前,这些成果表示CMOS驱动电路和功率MOSFET的单芯片集成是未来的趋势,器件性能优化以及集成度更高的工艺技术,将会持续推陈出新。UlOednc

UlOednc

UlOednc

图14:射月计划提出的CMOS驱动电路和VDMOSFET单芯片集成剖面结构示意图。UlOednc

综上所述,SiC器件在大功率应用已经是必然趋势。随着技术成熟、芯片尺寸增加,器件成本会持续下降,性价比提高的结果,产品渗透率会快速提升。至于SiC IC的发展还在研究初期,但是已经看见希望,关键还是在性能提升和成本降低,或许还要3~5年才会有实用的价值,需要研究单位积极投入。UlOednc

参考文献

- M. E. Levinshtein, S. L. Rumyantsev, and M. S. Shur, Eds., “Properties of Advanced Semiconductor Materials GaN, AlN, InN, BN, SiC, SiGe“ New York: Wiley, 2001, pp.31-47.

- A. Bolotnikov et al., "Overview of 1.2 kV – 2.2 kV SiC MOSFETs targeted for industrial power conversion applications," 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), 2015, pp. 2445-2452.

- F. Roccaforte, G. Greco and P. Fiorenza, "Processing Issues in SiC and GaN Power Devices Technology: The Cases of 4H-SiC Planar MOSFET and Recessed Hybrid GaN MISHEMT," 2018 International Semiconductor Conference (CAS), 2018, pp. 7-16.

- T. Kimoto, “Material science and device physics in SiC technology for high-voltage power devices,” Japaness J. Appl. Phys., vol.54, p.040103, 2015

- T. Nakamura, Y. Nakano, M. Aketa, R. Nakamura, S. Mitani, H. Sakairi, and Y. Yokotsuji, “High performance SiC trench devices with ultra-low ron,” in Proc. IEEE Int. Electron Devices Meeting (IEDM), 2011, pp.599-601.

- R. Siemieniec et al., "A SiC Trench MOSFET concept offering improved channel mobility and high reliability," 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, pp. P.1-P.13

- T. Kojima, S. Harada, Y. Kobayashi, M. Sometani, K. Ariyoshi, J. Senzaki, M. Takei, Y. Tanaka, and H. Okumura, “Self-aligned formation of the trench bottom shielding region in 4H-SiC trench gate MOSFET,” J. J. Appl. Phys., vol.55, 04ER02, 2016.

- H. Takaya, J. Morimoto, K. Hamada, T. Yamamoto, J. Sakakibara, “A 4H-SiC Trench MOSFET with Thick Bottom Oxide for Improving Characteristics, “in Proc. of Int. Symp. on Power Semi. Dev., 2013, pp.43-46.

- X. B. Chen US Patent 5216275.

- B. J. Baliga, Advanced Power MOSFET Concept, Springer, 2010

- M. Baba, T. Tawara, T. Morimoto, S. Harada, M. Takei and H. Kimura, "Ultra-Low Specific on-Resistance Achieved in 3.3 kV-Class SiC Superjunction MOSFET," 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2021, pp. 83-86.

- W. Xie, J. A. Cooper, and M. R. Melloch, “Monolithic NMOS digital integrated circuits in 6H-SiC,” IEEE Electron Device Lett., vol. 15, no. 11, pp. 455–457, Nov. 1994.

- D. M. Brown et al., “High temperature silicon carbide planar IC technology and first monolithic SiC operational amplifier IC,” in Proc. 2nd Int. High-Temperature Electron. Conf., 1994, pp. XI-17–XI-22.

- D. B. Slater et al., “Demonstration of 6H-SiC CMOStechnology,” in Proc. 3rd Int. High-Temperature Electron. Conf., 1996, pp. XVI-27–XVI-32.

- S. Ryu and K. T. Kornegay, “Design and fabrication of depletion load NMOS integrated circuits in 6H-SiC,” in Proc. Inst. Phys. Conf., London, U.K., 1996, pp. 789–792.

- J.-S. Chen, K. T. Kornegay, and S.-H. Ryu, “A silicon carbide CMOS intelligent gate driver circuit with stable operation over a wide temperature range,” IEEE J. Solid-State Circuits, vol. 34, no. 2, pp. 192–204, Feb. 1999.

- Brett A. Hull, Sei-Hyung Ryu, Husna Fatima, Jim Richmond, John W. Palmour, and James Scofield, “Development of A 4H-SiC CMOS Inverter,” Mater. Res. Soc. Symp. Proc. Vol. 911, B13-02, 2006.

- D. T. Clark, et al., “High Temperature Silicon Carbide CMOS Integrated Circuits,” Materials Science Forum, vol. 679-680, pp. 726-729, Mar 2011.

- E. P. Ramsay et al., “Digital and analogue integrated circuits in silicon carbide for high temperature operation,” in Proc. IMAPS High Temperature Electron. Conf., Albuquerque, NM, USA, 2012, pp. 373–377.

- R. A. R. Young, et al., “High Temperature Digital and Analogue Integrated Circuits in Slicion Carbide,” Materials Science Forum, vol. 740-742, pp. 1065-1068, Jan 2013.

- M. H. Weng, D. T. Clark, S. N. Wright, D. L. Gordon, M. A. Duncan, S. J. Kirkham, M. I. Idris, H. K. Chan, R. A. R. Young, E. P. Ramsay, N. G. Wright, and A. B. Horsfall, “Recent advance in high manufacturing readiness level and high temperature CMOS mixed-signal integrated circuits on silicon carbide,” Semicond. Sci. Technol. 32 (2017) 054003.

- N. Kuhns, L. Caley, A. Rahman, S. Ahmed, J. Di, H. A. Mantooth, A. M. Francis, and J. Holmes, “Complex High-Temperature CMOS Silicon Carbide Digital Circuit Designs,” IEEE Trans. on Devices and Materials Reliability, vol.16, no.2, 2016, pp.105-111.

- S. Roy, R. C. Murphree, A. Abbasi, A. Rahman, S. Ahmed, J. A. Gattis, A. Matt Francis, J. Holmes, H. A. Mantooth, and J Di, “A SiC CMOS Digitally Controlled PWM Generator for High-Temperature Applications,” IEEE Trans. on Industrial Electronics, vol.64, no.10, 2017, pp.8364-8372.

- M. Masunaga , S. Sato , R. Kuwana, N. Sugii, and A. Shima, “4H-SiC CMOS Transimpedance Amplifier of Gamma-Irradiation Resistance Over 1 MGy,” IEEE Transactions on Electron Devices, vol. 67, no. 1, pp. 224-229, Jan. 2020.

- J. -Y. Jiang, J. -C. Hung, K. -M. Lo, C. -F. Huang, K. -Y. Lee and B. -Y. Tsui, “Demonstration of CMOS Integration with High-voltage DMOS in 4H-SiC,” IEEE Electron Device Lett., vol.42, no.1, pp.78-81, 2021.

- M. Okamoto, A. Yao, H. Sato, and S. Harada , "First Demonstration of a Monolithic SiC Power IC Integrating a Vertical MOSFET with a CMOS Gate Buffer," in Proc. 33th Int. Symp. Power Semiconductor Devices ICs (ISPSD), Jun. 2021, pp. 71-74.

- B. Y. Tsui, C. L. Hung, T. K. Tsai, L. J. Lin, T. W. Wang, and P. H. Chen, “Dual Gate Oxide CMOS Process on 4H-SiC,” to be presented in the 2022 International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 2022.

- B. Y. Tsui, C. L. Hung, T. K. Tsai, Y. C. Tsui, T. W. Wang, Y. X. Wen, C. P. Shih, J. C. Wang, L. J. Lin, C. H. Wang, K. W. Chu, and P. H. Chen, “First Integration of 10 V CMOS Logic Circuit, 20 V Gate Driver, and 600 V VDMOSFET on a 4H-SiC Single Chip,” to be presented in the 34th IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD), 2022.

闳康编辑室后记

以碳化硅(SiC)与氮化镓(GaN)为材料的第三类半导体,相较于传统硅基半导体器件,不仅能够承受更高的功率、频率及环境温度,同时也拥有良好的散热特性,因此在5G基站、电动汽车、低轨卫星、太阳能或工业4.0等高值化产业中,具有绝对的技术应用优势。过去受限于第三类半导体的晶圆制造困难、并且价格昂贵,使得其仅能用于国防或航天等领域。直到近几年,才因为技术进展得以大幅降低生产成本,普及应用到工业、汽车与消费类电子等产业。UlOednc

目前碳化硅半导体器件前三大应用占比分别为电动汽车61%、太阳能发电及储能13%、及充电桩9%。其相较于原本以硅为基础的功率器件,能提供更高效率的电子转换能力,带来更好的节能效果。根据TrendForce市调预估,自2020年至2025年,碳化硅器件应用市场将由6.8亿美元成长到33.9亿美元,年复合成长率(CAGR)高达38%。即使这几年碳化硅半导体的市场规模仍小,但随着全球电动汽车与能源应用的产业需求推进,其必然很快成为半导体领域发展的新契机。UlOednc

台湾阳明交大崔秉钺教授及其实验室团队是台湾第三类半导体技术的知名研究团队。自2018年起,该团队即参与“半导体射月计划——碳化硅单芯片功率系统平台”研发项目的执行。期间除了产出许多创新研究成果外,也积极与业界共同合作,落实研发成果的产业化应用,其对于提升台湾在第三类半导体领域的核心竞争优势,具有极大的贡献。闳康科技非常荣幸今年度可以和崔教授携手进行产学合作,提供该团队在碳化硅功率器件及相关集成模块研究上所需之完整分析服务。闳康科技拥有完备的检测设备与专业技术经验,能全面满足化合物半导体在工艺、封装及失效分析方面之各种分析检测需求。UlOednc

闳康相关分析技术请参考:UlOednc

3D光学显微镜https://www.ma-tek.com/zh-CN/services/index/3D-OMUlOednc

探针电性测量https://www.ma-tek.com/zh-CN/services/index/I-VUlOednc

TEM试片制备https://www.ma-tek.com/zh-CN/services/index/TEM-sampleUlOednc

TEM穿透式电子显微镜https://www.ma-tek.com/zh-CN/services/index/TEMUlOednc

EDX能量散射X射线谱https://www.ma-tek.com/zh-CN/Tech_Article/detail/MA/all/202103UlOednc

本文为《电子技术设计》2022年4月刊杂志文章,版权所有,禁止转载。免费杂志订阅申请点击这里。UlOednc

责编:Demi

最前沿的电子设计资讯

最前沿的电子设计资讯