在本系列的第一篇文章中,我们探讨了高速电压反馈运算放大器(VFA)的I/O范围选择。这里我们将针对其余两种最常用的高速放大器探讨相同的问题。首先是“电流反馈放大器”(CFA),然后是“全差分放大器”(FDA)。CFA的I/O问题比较简单,而FDA却有许多新的I/O范围问题和新功能。我们将通过一些基本应用以及一些具有代表性的详细选择参数来阐述这两种放大器的I/O范围问题。

20世纪80年代初,Comlinear公司推出首批CFA混合器件。其拓扑结构极大地受益于对称的NPN和PNP器件,而垂直型PNP IC工艺在20世纪80年代中后期才开始出现。Comlinear的第一款单片CFA(CLC400)在1988年10月推出,比另外两款单片CFA(AD811和EL2020)的时间晚几个月。30年来不断有新的CFA推向市场,但其输入范围却始终不包含任何一个电源轨。

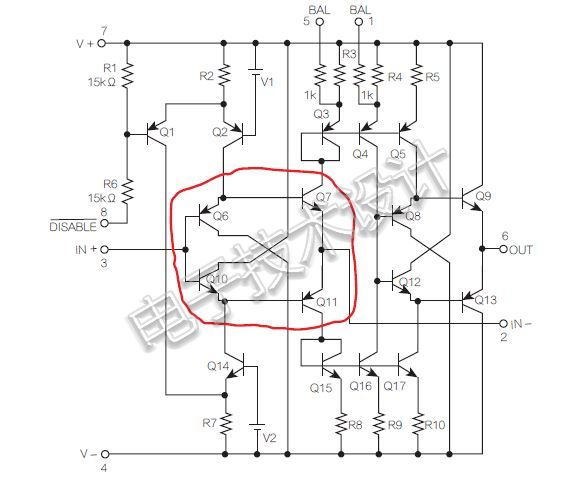

在典型的运算放大器图中,CFA的V+~V-引脚之间需要一个单位增益缓冲器。然而,此V-(图1中的In-)引脚也需要通过电流镜将双极性误差电流上下传递给每个电源。要使此阴极级联(cascode)误差电流(“反馈电流”)通过V-节点上的射极跟随器上下传递到电源附近的电流镜,对于此单位增益缓冲器,就需要从V+输入到V-节点相对电源有一定的净空。图1是一个典型的CFA电路图,其中突出的部分是一个非常简单的输入缓冲器。虽然这款早期的CFA器件还乐观地包含了偏置平衡引脚(借鉴了VFA IC设计),但此外部平衡调整无助于改善输出偏置漂移,所以在后续的CFA器件中很少采用。

图1:早期CFA单片运算放大器(EL2020)电路图。

同样,虽然有少数CFA器件是轨到轨输出(RRO),但其它所有CFA都是非RRO。输入缓冲器比大多数输出级需要更大的净空。这表示产品的输出相对输入引脚具有较小的净空值选择(而且I/O到每个电源对称)。到目前为止,CFA的主要应用是提供一些同相增益(或反相运行),所以输入端增加的净空不是输出摆动的限制因素。

虽然所有CFA器件本质上都是单位增益稳定的,但由于许多应用的同相增益较高,因此许多器件指定增益为+2V/V,有时更高。理论上,CFA的AC性能可以保持不变。然而,工作在较高同相增益的输入缓冲器两端所需的较低电压摆幅范围(或在反相的情况中输入缓冲器两端没有电压摆动),会将全功率带宽(FPBW)极限转移到主放大器而不是输入端之间的开环缓冲器。

因此,相对于更普遍的VFA解决方案,CFA解决方案又会应用在哪里?VFA器件一般用在ADC之前,而CFA则主要用在DAC之后提供信号发生器功能。由于CFA的压摆率可以按需要调整(slew rate on demand),因此在大信号线性度对静态功耗方面比VFA具有显著优势。早期的CFA应用多是增益为+2V/V的简单视频线驱动器,用来恢复视频同轴传输的反向匹配损耗(backmatch loss)。与此同时,CFA放大器最初应用于HP任意波形发生器(AWG)输出级,而许多信号发生器继续在输出BNC或SMA连接器后面使用CFA器件。

20世纪90年代中期,用于数字用户线(xDSL)的各种双绞线线路驱动器的面世,给双通道CFA带来了极大的机会,推动了通用双CFA器件的产品开发。与两个独立的运算放大器不同,最新开发的有线驱动器是专用的,只适于差分驱动器应用。比如在xDSL、PLC、G.Fast和智能电网等各种有线通信技术中,核心CFA用作差分输出驱动器无处不在。双耦合CFA在数据手册中通常称为“端口”,表示一对固定的推挽式CFA驱动器。

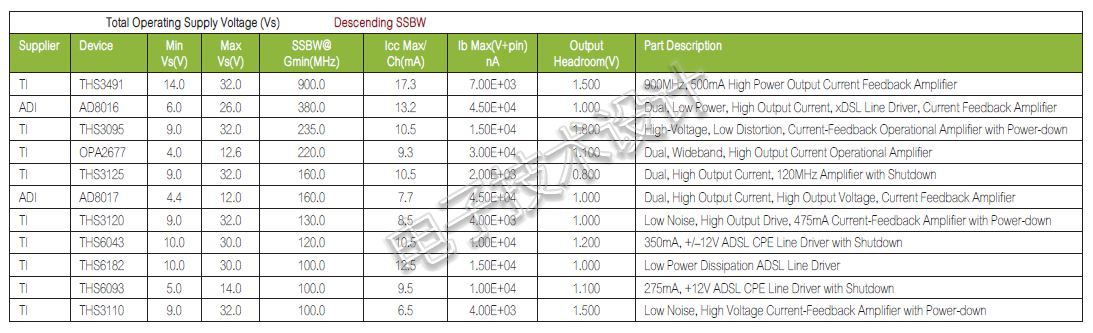

具有较高输出电流的CFA通常应用于AWG和有线通信中。第一个CFA表筛选了>200mA的线性输出电流,包括单通道(AWG)和双通道(xDSL)。有些双通道CFA线路驱动器甚至不提供单通道版本。此外,某些只能用作差分推挽输出级的双通道CFA没有包含在表1中。这里列出的双通道CFA可用于负载共享配置,也可以单独用于单端线路驱动器。

为显示较新的高输出电流CFA,表1还根据以下条件进行了筛选:

1. 输出净空>2V

2. 若禁用和非禁用器件有不同的产品型号,则只列出禁用版本

3. 输入电压噪声<4nV/√Hz

4. 内部增益值固定

5. 过时的器件

表1: 高输出电流单通道、双通道CFA器件。

目前最快的高输出电流CFA是最近推出的THS3491,它用于AWG输出。注意,这里较高的最大Vs通常支持AWG或有线驱动器的较高输出电压摆动。

在低输出功率应用中CFA器件更多,包括许多单/双/四通道系列。另外,所有这些器件都是非RRIO,所以输入与输出通常要求更多的净空。为简单起见,表2仅列出单通道器件,筛选条件与表1相同。

表2: 具有代表性的通用单通道CFA。

这些器件采用了图1中的原始CFA设计,其中一个器件(OPA684)用了一个闭环输入缓冲器,在低功耗器件增益设置下提供更加恒定的带宽。闭环输入缓冲级可降低从V-输入端看进去的开环阻抗,从而减少环路增益公式中的寄生效应。表2所列器件的最大工作电源电压有很多相似之处,表明其所使用的互补双极工艺技术是相似的。从Ib max这一列来看,表中没有CMOS CFA器件。V+输入偏置电流始终是两个偏置电流的抵消。V-输入偏置电流通常较高且与V+偏置电流无关,除非采用偏置电流抵消技术改善输出偏置。

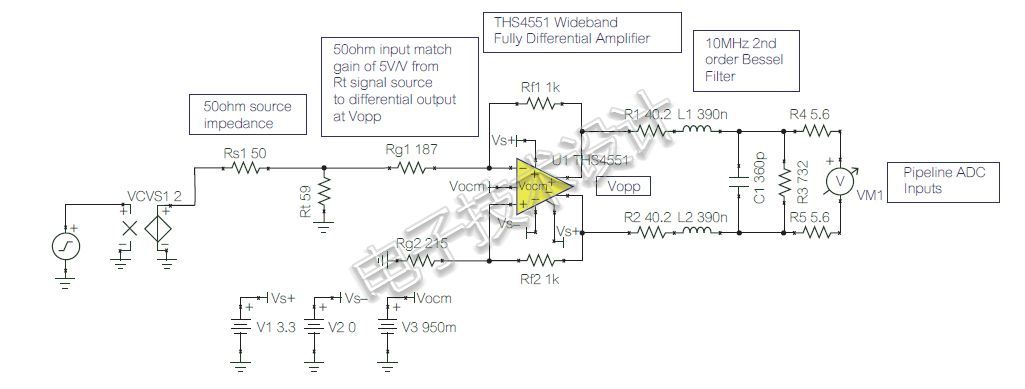

自1999年面世以来,FDA已成为驱动差分输入ADC的常用方法。简言之,FDA是具有第二共模控制环路的核心差分I/O运算放大器。第二环路测出两个输出电压的平均值,并迫使它去匹配一个所加的(通常为DC)Vocm输入电压。不熟悉FDA的可通过图2中显示的典型直流耦合、单端转差分ADC驱动器设计来了解,它采用了最近推出的NRI、RRO精密FDA。

图2:直流耦合,3.3V单电源,双极性单端源5V/V增益。

FDA的一个新功能是取得一个接近地的直流耦合双极性输入摆动,并使用单电源解决方案,将其移动至接近所需共模电压的差分输出摆动。两个输入引脚上的电压总是经过电平转换后高于地。在图2的单端输入例子中,当源信号处在中间水平时,两个输入引脚上会产生一个平均电压,它会以共模电压的形式随信号而上下移动。要想看到这种效果,一种比较容易的办法是注意下方的FDA输出端的反馈通路。工作在单电源时,FDA输出不会低于地。

因此,分压器回到下方输入反馈引脚的电压也不会低于地。差分环路将输入差分电压强制为零,从而在两个输入引脚上产生相同的共模移动。查看输入引脚共模移动最容易的办法,是通过Rg/(Rf+Rg)对下方的FDA(非信号输入端)输出电压摆幅进行简单的电阻分压。近期的FDA更多的是采用负轨输入(NRI),通过一个单电源将双极性或地参考输入信号转换为DC耦合差分输出来实现这种简单操作。

为了获得此NRI,许多FDA使用核心VFA拓扑(带PNP输入)来实现与更多典型VFA器件的I/O范围选择相匹配的信号通路。有少数FDA器件,它们使用非RRIO的核心CFA设计。FDA的一个新的考虑因素是内部共模控制电路所需的工作净空。所有FDA都增加了一个用于设置输出共模电压(图2中的Vocm)的控制电压输入。

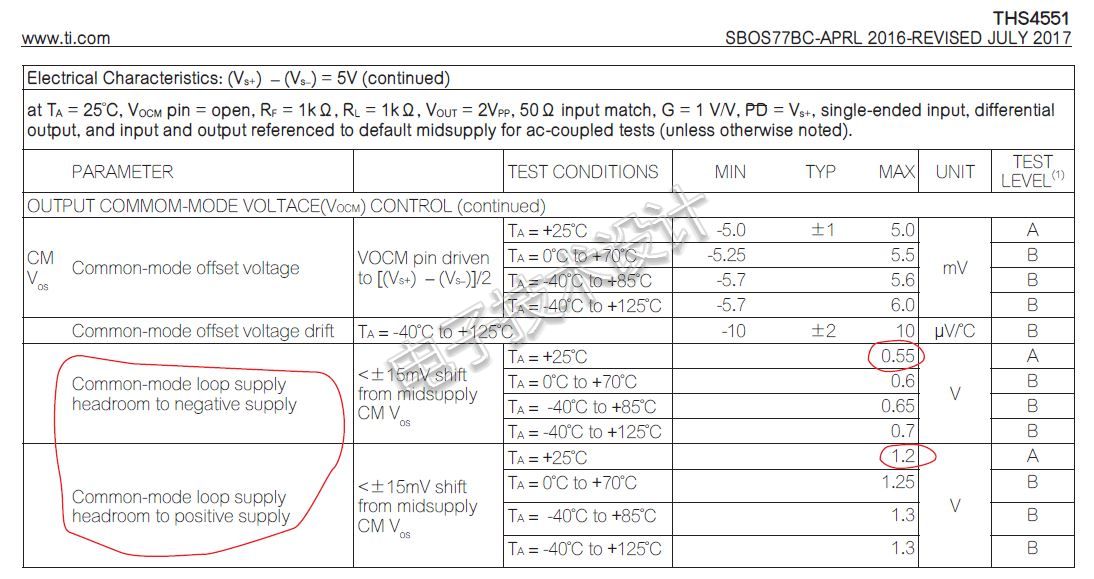

由于这两个输出引脚需要围绕此电压进行差分摆动,因此没有FDA会提供包含电源的输出共模电压范围。对于共模范围,典型的情况是对负电源的净空比对正电源的净空小。FDA所采用的工作单电源,其输出共模电压转移至更接近地电平(0.95V,典型的流水线ADC Vcm,如图2所示),以满足ADC要求。图3显示了一个最新的精密FDA的典型共模控制电压净空规格。

图3:NRI、RRO FDA的典型共模环路净空规格。

FDA应用的设计流程从输出引脚开始,然后回推到输入。首先,输出共模电压设置为ADC所需的电压。对于交流耦合输出应用,Vocm输入引脚通常可以悬空,许多FDA默认其电压值为中间电源,从而在该Vocm(两个电源电压的中间值)周围提供最大的差分输出摆动。这种情况下,在这些输出阻塞电容的另一侧会重新建立ADC所需的共模。

评估输出摆幅限值的第一步是以相反极性在Vocm电压周围加减差分峰值Vpp/4摆动。每个输出端提供1/2总Vpp,然后每个引脚又围绕Vocm电压摆动其±1/2,以产生全差分摆动。然后将最小/最大绝对输出电压范围与电源的输出净空进行比较,以验证输出信号不出现削波。

FDA的最新考虑(也是难点)在于输入引脚电压作用之处。简而言之,假设平衡电阻分压器在FDA的两侧,差分输入设计会以固定的DC FDA输入引脚电压工作,该电压是源共模电压和FDA设置输出共模电压分压的结果。无论在输入端是采用直流耦合还是交流耦合作为差分输出的单端输入,FDA的一个令人困惑的地方是,FDA输入引脚上的电压都会通过共模检测随着输入信号移动。回到图2的例子:

1. 输出共模电压为0.95V,由Vocm输入电压设定。

2. FDA引脚上的目标最大差分输出为2Vpp,对于典型的流水线ADC,由低插入损耗滤波器衰减到1.8Vpp的-1dBFS幅度。注意在滤波器末端使用差分R来维持FDA到ADC的共模输出为0.95V。

3. 然后每个FDA输出引脚摆动0.95±0.5V,或者从0.45V至1.45V。该RRO FDA需要大约0.2V的输出净空——使用3.3V单电源限幅这些输出摆动不会出现削波。

4. 为得到增益5,在Rt上需要±0.2V双极性输入,以达到相应的输出电压。

5. FDA输入引脚以共模方式移动(215Ω/(1kΩ+215Ω))*(0.45V →1.45V)或0.08V→0.256V(FDA下侧对地输出摆动通过电阻分压器对下侧反馈通路进行分压后送到输入引脚)

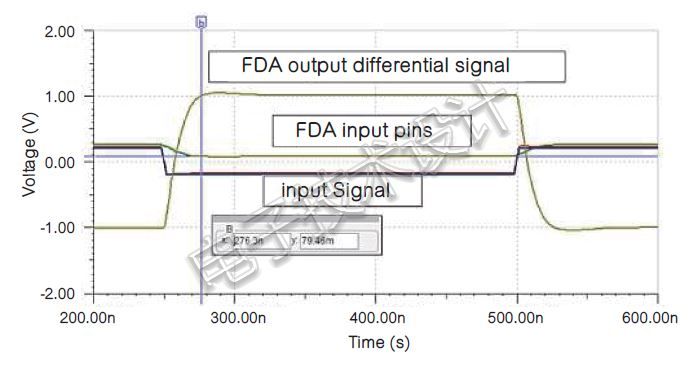

使用TINA对图2中的电路进行2MHz方波响应仿真,得到图4的波形。图中输入引脚低电平处的记号(marker)显示了预期的80mV最小值。重点是输入引脚保持在地之上,在NRI FDA的范围内。请记住,差分2Vpp输出信号实际上是2个0.45V至1.45V摆幅,

图4:图2中Rt处施加2MHz±0.2V输入进行方波仿真。

这个示例显示了I/O引脚的工作条件。早期的开发允许使用不平衡反馈分压器,从而使公式变得复杂。假设在每个反馈通路上使用匹配的分压器(AC和DC),可大大简化这种情况,并且更能代表预期的应用。随着不平衡方法的发展,反馈分压器不平衡的影响也显露出来。

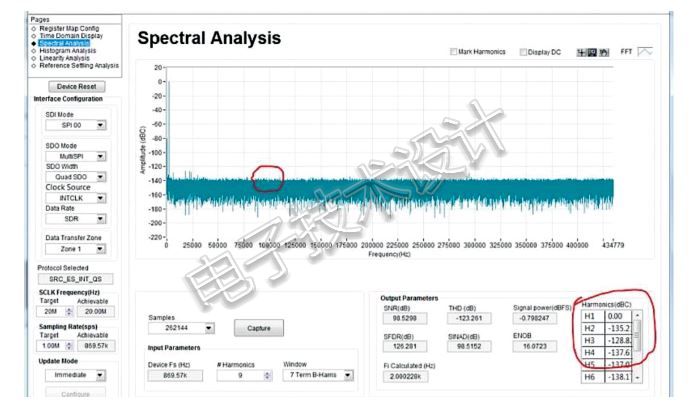

正如在VFA运算放大器的I/O范围选择中提到的,使用-0.23V LM7705固定稳压器可以实现单电源RRO器件真正摆动到地(良好的线性度或SFDR)。由于开关纹波问题(LM7705在92kHz时为4mVpp),设计人员通常会避免这种选择。像THS4551这样的精密FDA,由于其差分输出结构,因而具有很好的PSRR。

参考文献《Optimized Analog Front End DAQ System Reference Design for 18-bit SAR Data Converters》的设计示例中使用了18位SAR ADC来测试这种组合解决方案。每个FDA输出引脚上使用0V→4.096V摆动,为该18位、1MSPS、SAR ADC提供总共8.192Vpp的最大差分输入。将4mVpp负电源纹波衰减100dB -PSR,由于存在电源纹波,仅得到40nVpp的差分输出。这远远低于(8.192V/(219))=15.6μV1/2 LSB,92kHz附近的电源纹波在FFT中应该是不可见的。该参考文献中提出了一系列问题,最后显示了一个2kHz满量程输入FFT,但在92kHz附近什么也没有。那个结果在这里又出现了,如图5所示,2kHz满量程输入的谐波项也非常低,表明这些新的低功耗FDA能够很好地驱动精密ADC。

图5:LM7705开关、-0.23V电源下THS4551信号通路的FFT。

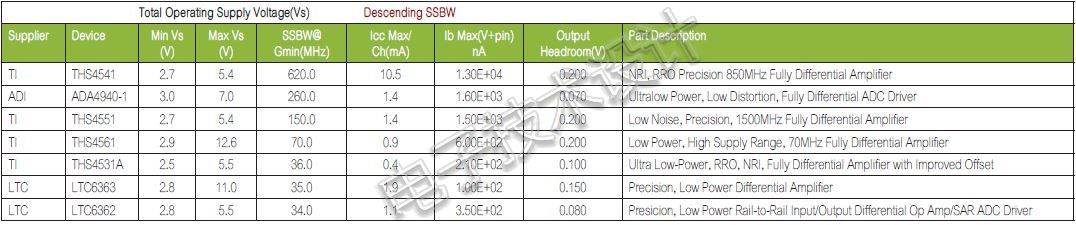

最新的FDA器件分为用于精密ADC驱动器的器件和更专注于高速流水线ADC的器件。精密FDA器件都是RRO,并且大多数是NRI。也有一些是RRI,能提供更低的输入引脚至正电源的净空。有些应用是将输入引脚移动到靠近正电源,其中高共模正电压的衰减可能为1。还有更多只需要NRI性能的应用,具有双极性或地至某正输入摆幅。

表3显示了基于VFA的精密RRO FDA器件,筛选条件如下:

1. 仅限单版本(许多都有双版本)

2. 最大输入失调电压<1mV

3. 为得到更新的器件,1k价格<$3.00

4. 没有固定增益版本

5. 没有过时的器件

表3:精密RRO FDA器件。

随着工作带宽的增加,FDA已经出现在I/O范围性能的每种组合中。其中许多设计具有较高的最小增益(VFA最小稳定增益),以获得较高的闭环带宽,LTC在LTC6404系列中甚至提供了一些最小增益。许多极高BW应用都是AC耦合的,因此较差的输入DC失调电压也能被一些FDA接受。在最高的SSBW时都不是RRO,但有一些是NRI,以处理极高速的DC耦合脉冲应用,其输入信号对+Vin来说是地。

甚至还有一些器件不是RRO,却是RRI。不过这些几乎都是基于VFA的,只有两个基于CFA的器件(LMH6554和ADA4927-1),这两个器件都是非RRIO,是典型的CFA设计。正如所料,这些CFA型FDA通常出现在差分输出AWG应用中。为了精简内容,表4仅列出单通道版本,并筛选出以下内容:

表4:最高速FDA。

这些都是双极型(通常是互补)IC工艺。注意,由于最大Icc的大幅增加,使提供的FDA在最高速度范围内。非完全补偿VFA ISL55210和基于CFA的LMH6554器件中出现了0.9nV/√Hz的最低输入电压噪声,后者实际上显示出更高的总输出噪声,因为CFA设计本身固有的电流噪声较高。

CFA对于大功率输出驱动器具有很大优势,但在输出端通常没有摆动到轨,并且两个轨始终不在输入引脚上。这几乎不会限制其作为AWG输出级或大功率差分线性驱动器的使用。最新推出的高速放大器中大多是FDA,其中基于VFA的版本提供了和VFA型运算放大器类似的I/O范围选择。

最近的多数工作集中在NRI、RRO精密器件,或具有非RRO和非RRI(或NRI)输入级的更高速FDA器件。最高闭环带宽需要非RRO输出级,但一些应用却受益于输入摆动更接近负电源。在图2的直流耦合双极输入示例中,如果FDA输入范围延伸到地,则一个新功能是利用FDA实现从双极输入到差分输出的单电源工作。

(原文刊登在ASPENCORE旗下Planet Analog美国网站,参考链接:Input and Output Voltage Range Issues for High Speed CFAs and FDAs。)

最前沿的电子设计资讯

最前沿的电子设计资讯