在现代电子测量、雷达、通信系统等技术领域中,具有频率范围宽,分辨率高,转换快速的多重模式的信号源是非常重要与必不可少的存在。尽管在上个世纪70年代,我们大都采用锁相频率合成技术实现频率范围为DC(MHz)~几十GHz,分辨率达到MHz的信号源,并且也已广泛应用到现代电子系统中,但其转换速度确实还不够高(几十μs到ms量级)。直至到了90年代,出现了频率分辨率高(MHz量级)、频率转换快(μs到ns量级)的直接数字频率合成(DDS)。其输出信号的频率上限基本在HF或VHF频段内,相比于PLL合成技术以及直接模拟合成技术所得到的信号频率都要低。可当我们既需要有高的频率分辨率,又要求较快的转换速度和较低噪声的超高频甚至微波信号时,怎样的选择才会使得技术更加具有优势呢?

锁相环电路存在于各种高频应用中。从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器中都有它的影子。而随着数字技术在仪器仪表和通信系统中的广泛使用,可从参考频率源产生多个频率的数字控制方法诞生了——直接数字频率合成(DDS)。

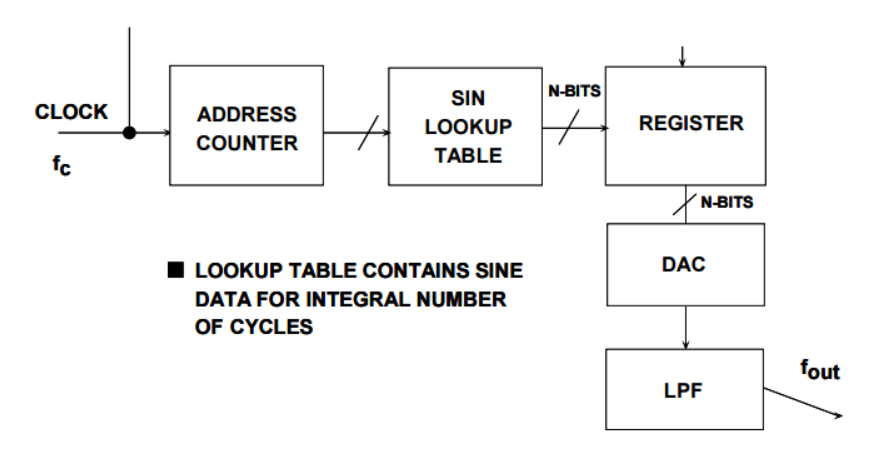

直接数字频率合成系统的基本原理

事实上,企业里的大多数工程师在求学时都接触过PLL,但DDS并不是普遍教授的内容。它们各自都有何具体优势呢?为了使它们都能在工具箱里具有恰当的“一席之位”,并帮助设计师快速确定一个最佳解决方案,此处附上表格供大家参考:

从表中我们可以发现:PLL在功耗上的优势很大程度取决于合成的频率范围。而对于DDS来说,由于它有很多数字成分,当提高采样速率时,功耗会显著增加,所以需要较高采样速率才能达到较高输出频率。如果频率在100 MHz以下,那么功耗的优势将具备相当的竞争力。以ADI公司的DDS产品AD9913为例,最高速度为250 MSPS、功耗约为50 mW (AD9913),因此DDS和PLL在这方面的差距不一定很大。随着工艺几何尺寸缩小,功耗差距也会缩小。

对于频率捷变性,我们都知道很多应用只需要一个稳定的输出频率。然而有些应用需要在不同频率之间跳跃,还有些应用需要看到一个慢速变化的频率。PLL有办法引入变化的频率,但却不便控制,而且可重复性也不如DDS提供的数字方法。跳频虽然可以利用两个并行PLL和一个开关来实现,但需要为每个可能希望调到的频率使用一个完整PLL,或者留出一定的建立时间以便改变旁路PLL的频率。(当然,也可以利用环路中的可变分频器扫频,但这样做的可控性或可重复性仍然远不如DDS扫频。)

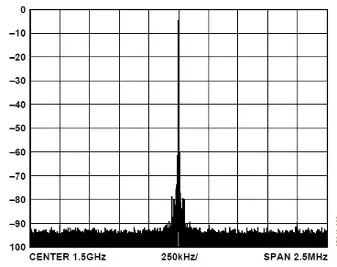

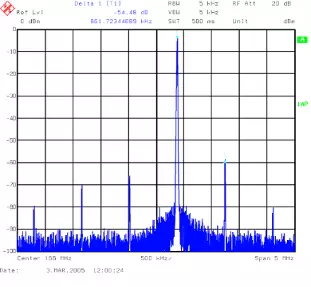

频谱纯度对比。如果需要小数N分频PLL,您会看到差距有所缩小,但不会完全消失。下图对宽频谱纯度作出了简单直观的说明。虽然它并不是一一对应的比较,但可以明显观察到:相比于PLL,DDS的输出频率中有更多(且更大)的频率杂散。关于可编程模数DDS的频率杂散值得注意的是,如果频率公式的分母中使用较小的整数值,您会看到杂散明显融合,杂散数量大大减少。从根本上讲,困境在于选择宽频谱纯度抑或选择调谐分辨率。

基于PLL的设计示例(摘自AD9510数据手册)

基于DDS的设计示例(AD9911所测数据)

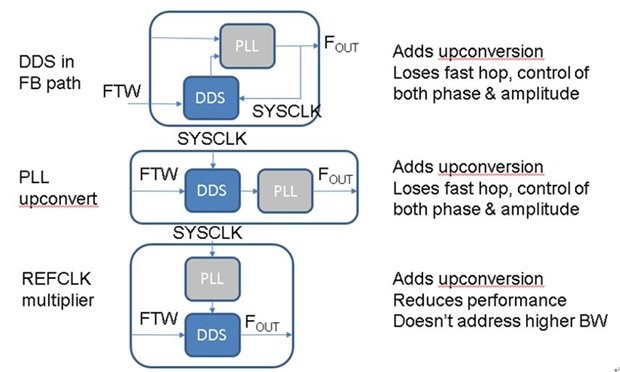

至于上变频,这儿给出两种方式。直接使用来自DDS的超奈奎斯特镜像频率,而不使用基频可降低信号输出功率,可使滤波器设计更加复杂(但必须设计一个带通滤波器,而不是低通滤波器。)另一个办法是DDS和PLL混用,从而同时获得二者的优势。

鉴于以上不同的特性,因此在价格上DDS与PLL必然也会存在差异。但随着几何尺寸缩小,这一差距也会缩小。相对来讲,PLL的使用更广泛,生产规模也要大很多,重点在于它有助于改善成本结构。而如果针对大规模应用,并且在DDS方案上存在着一些优势,那么在价格上应该会存在协商空间。考虑到此,既然两者都各有优势,如果能相互取长补短,实现双优兼用岂不更好?

ADI有一款运行速度为400 MSPS的DDS (AD9956),它是一款完整的直接数字频率合成器,由一个DDS和PLL电路组成。使用48位调谐字,其调谐分辨率不低于1.42 µHz(请注意单位,微赫兹),而一般标准PLL的分辨率因受限于环路中分频器的深度,其分辨率比这个要差好几个数量级。虽然我们都知道,小数 N分频 PLL(N为PLL中反馈分频器的分频系数)能够显著缩小该差距。但使用小数N分频PLL有弊端:输出中杂散会更多,信号抖动也会更厉害。

此外,标准DDS无法达到许多精确比率。在标准DDS频率公式中,分母总是2的幂。例如,若采样时钟为200 MHz,您可以精确地获得50 MHz频率(/4),但不能精确地获得40 MHz频率——会有一点偏差。而如果你使用的是ADI旗下的AD9956,那么结果要么比 40 MHz 少 0.142uHz,要么比 40 MHz 多 0.568uHz。

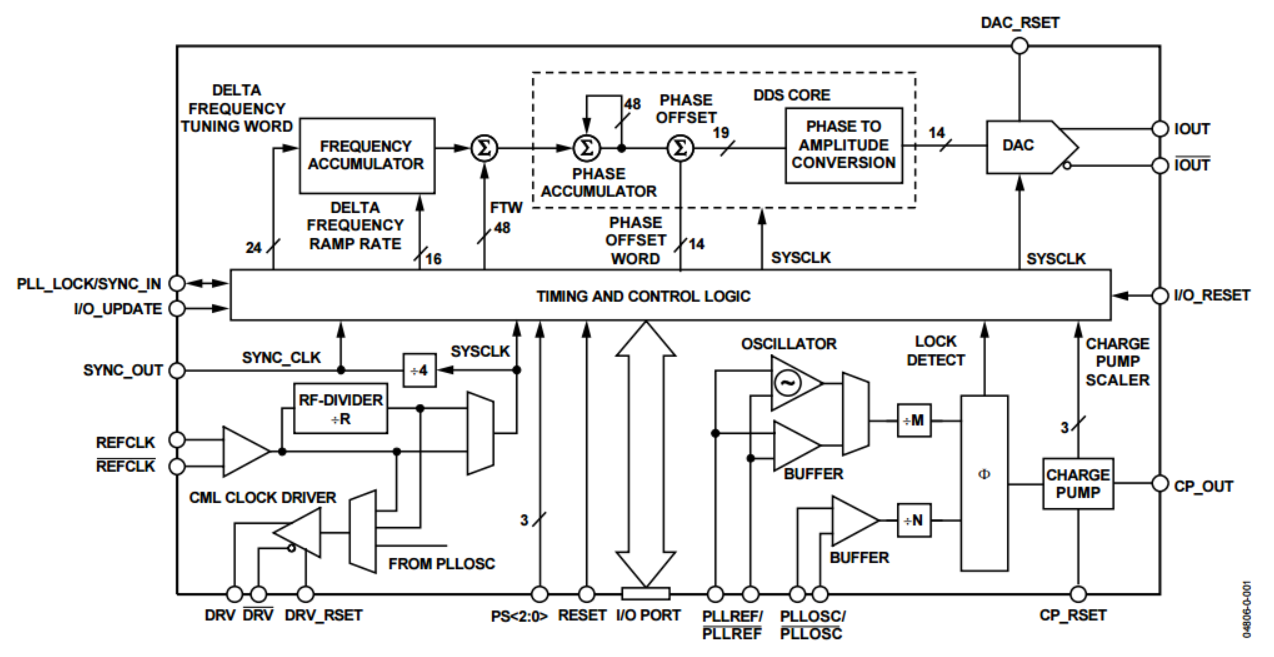

AD9956功能结构图

同样地,在DDS中看起来比较劣势的精密比率问题,标准PLL可以非常轻松地实现。因此,当真正需要精确的比率时,应避免使用标准DDS。但是,这不能并不意味着需要全然规避DDS。DDS也有它的优势,比如可编程模数!

可编程模数DDS(这里称为 P-MOD)是DDS领域一项相对较近的创新。它允许改变DDS公式,使分母不再局限于2的幂。因此,任何PLL在频率分辨率上都不及P-MOD DDS(如AD9913、AD9914、AD9915、AD9164),这是它的固有特性使然。勤奋的工程师对于AD9956可能会设计一个采用跳频的系统,80%的时间位于比40 MHz低一点的频率,20%的时间位于比40 MHz高一点的频率,这样不仅能得到一个平均频率为40 MHz的信号,而且模仿了P-MOD的内部工作机制。

自上个世纪30年代频率合成理论被提出以来,频率合成技术就已不断取得迅速的发展,逐渐形成了直接频率合成技术、锁相频率合成技术、直接数字式频率合成技术三种基本频率合成方法。这些技术都是近代电子系统和装备的重要组成部分,在无线电技术和电子系统的各个领域均得到了广泛的应用。ADI作为世界领先的高性能模拟技术公司,其在频率合成技术方向上自然走得远。因此在通信、测试设备和雷达系统等领域也拥有最理想、最灵活的解决方案。

最前沿的电子设计资讯

最前沿的电子设计资讯