在今天由ASPENCORE旗下《电子工程专辑》、《电子技术设计》、《国际电子商情》三大媒体联合举办的“2019年中国IC领袖峰会”上, Imagination中国资深市场拓展经理郑魁给我们带来了题为“加速AI IC设计产业化, 引领边缘智能行业发展”的主题演讲,分享了AI产业化及边缘智能化过程中遇到的一些挑战 。

本届中国IC领袖峰会特别鸣谢赞助商:上海兆芯; Cadence; Arrow; 深圳市中微半导体;华虹宏力; Mentor,a Siemens Business ; Imagination; 泰凌微电子;北京晶宇兴;华大九天;紫光展锐;比亚迪微电子。

随着5G网络的部署,以及端侧计算能力的提升,我们看到计算从云到端迁移的趋势,并且伴随着边云协同计算架构的快速演进。在这个演进过程中,我们发现,由于端侧应用非常多样化,对我们计算能力可扩展性提出了更高的要求。而且,随着AI算法快速迭代,对我们计算平台的算力灵活性以及标准化也是提出了更高的要求。

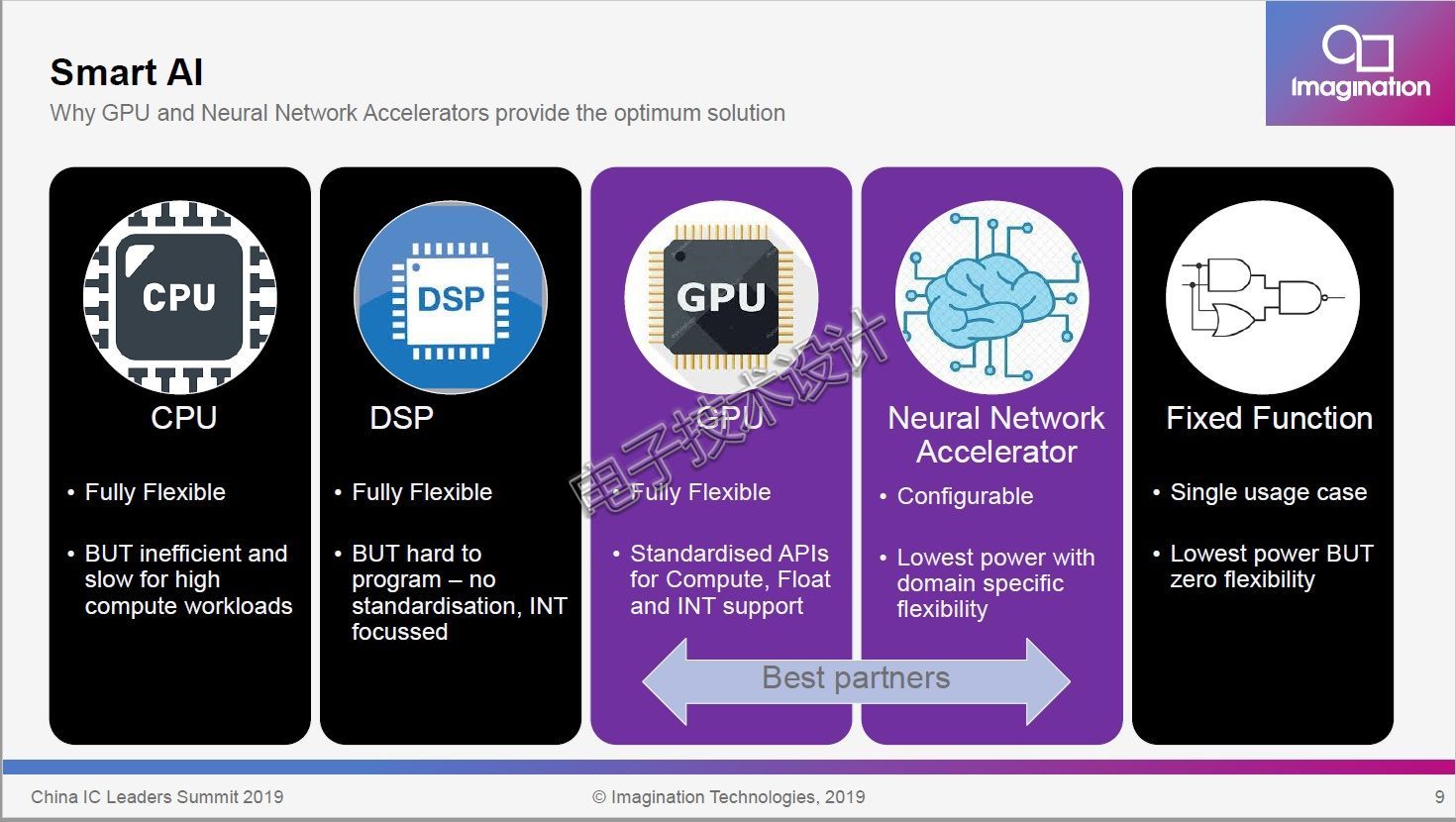

Imagination基于统一的软件架构,推出了基于PowerVR传统的GPU,以及PowerVR的计算机视觉和AI加速器的组合,希望通过这样的异构架构,我们可以为应用开发提供更灵活的算力。

“我们认为未来AI应用的落地,关键应该是在软件,在这些应用上面。我们提供的硬件平台需要对应用开发者更加友好,让开发者去掌控他所需的算力。因此,在做芯片设计时,需要考虑的不仅仅是性能、功耗、面积这样传统的维度,还需要考虑灵活性这种新的维度。”郑魁表示。

“利用最新的网络加速器,可以支持最通用的网络,同时在PPA上达到最佳的平衡。通过GPU,包括通过利用可编程的标准接口,我们给开发者很大的开发空间,让他们开发自己新的网络,进行算法迭代。”

“我们提供了NNA(神经网络加速器)+GPU(图形处理器)的组合,在性能提升的同时,又可以提供更大的灵活性。”他补充说。

随着提供更好的算力和应用,安全性成为一个非常关键的因素。Imagination最新的网络加速器不仅可以保护网络模型,包括权重和中间数据,还可以保护算法公司的成果,同时可以保护内容。

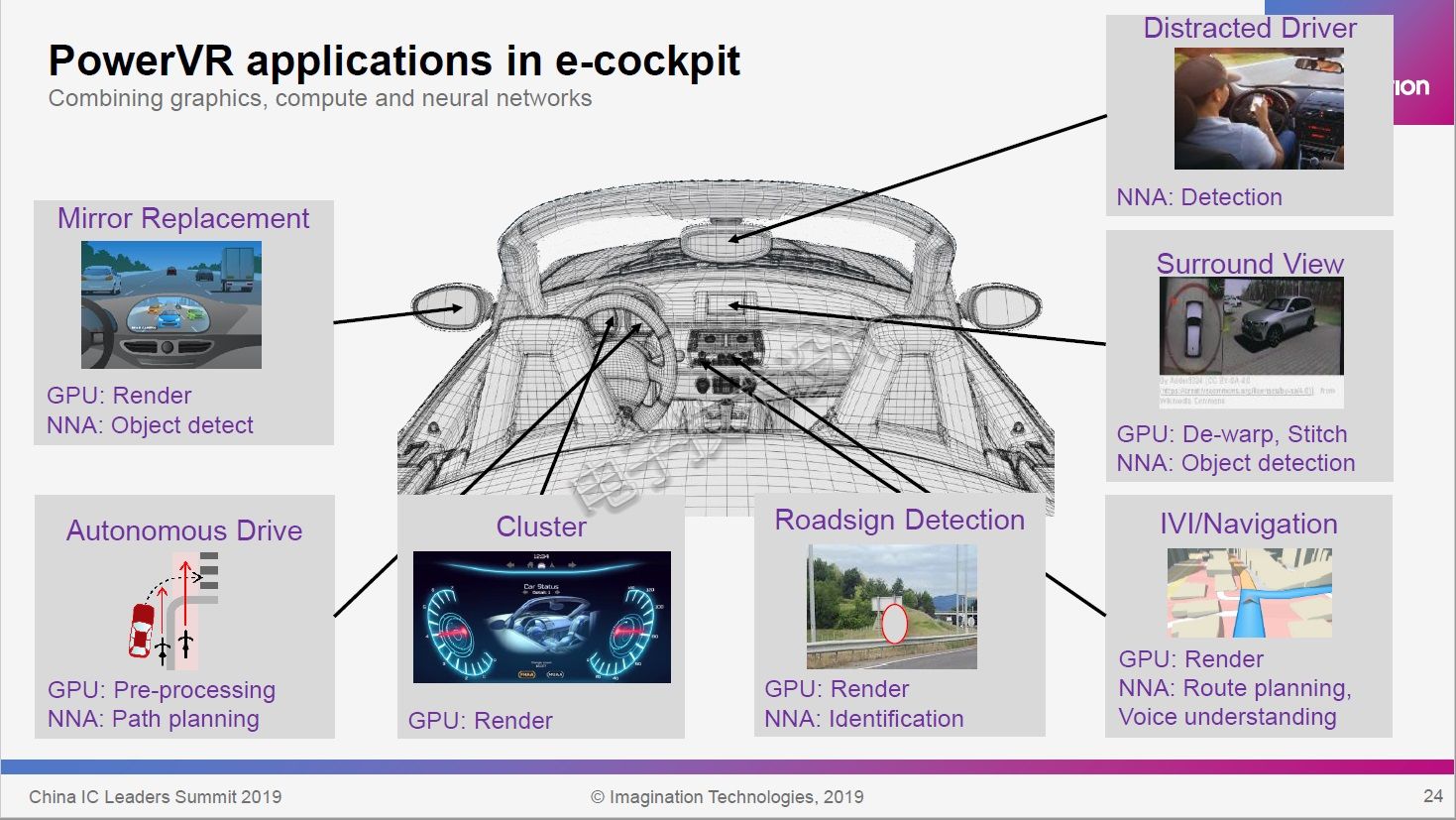

随着智能交互领域的一些新技术革新,对GPU显示的需求越来越多,比如智能驾舱。“我们需要通过GPU虚拟化技术,对系统安全性提供保障,在未来交互领域,即使主控GPU出现问题,也不会影响仪表盘或其它重要显示屏的内容输出。”他表示。

基于PowerVR的GPU虚拟技术,通过硬件可以提供8个虚拟机,完全满足了智能驾舱的主控屏、仪表盘以及后座椅分屏的显示。Imagination会提供足够的安全保障,当一个屏有问题的时候不会影响其他屏的工作。

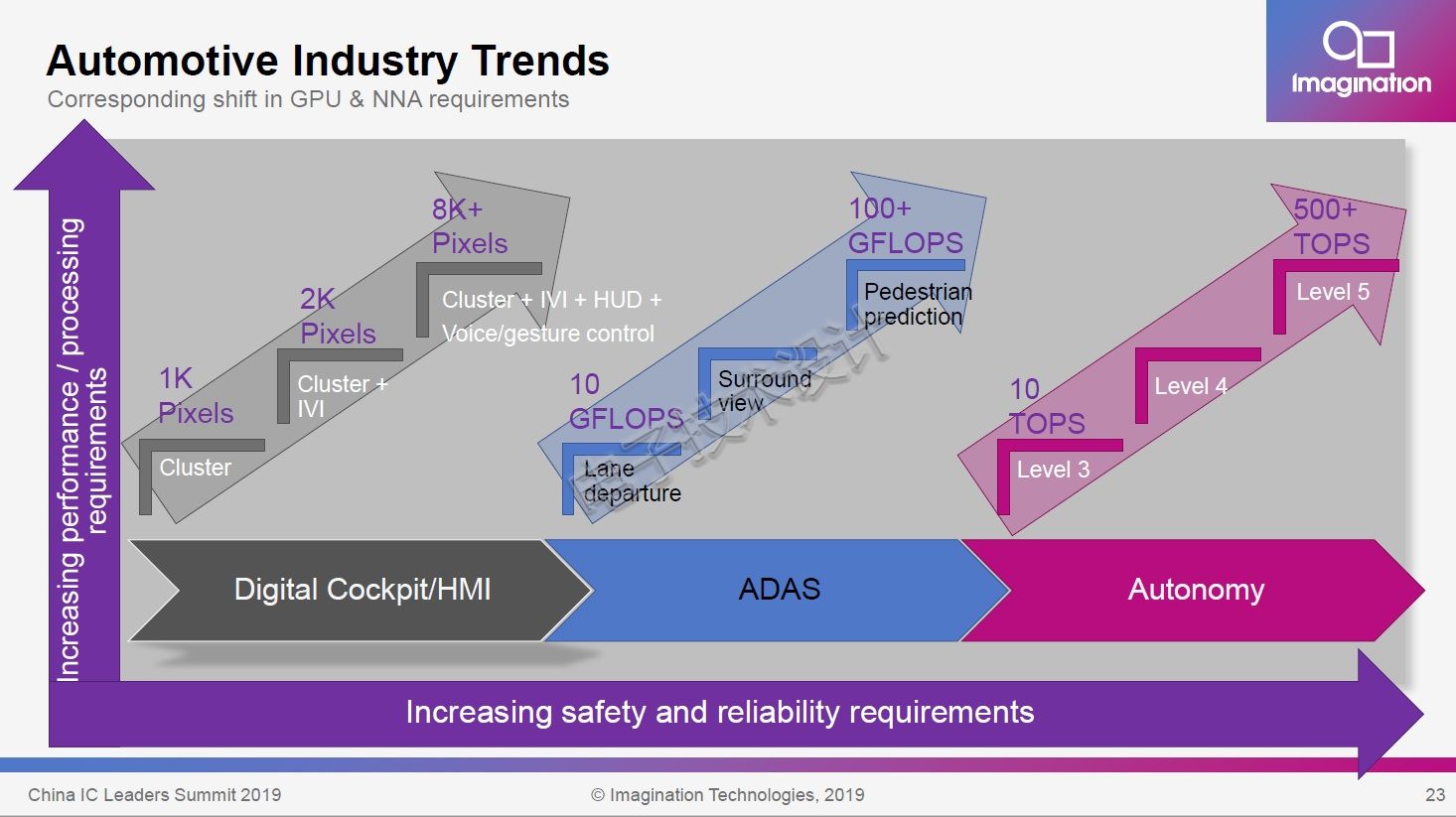

针对汽车的智能化,我们可以分成三个领域:首先是智能驾舱,也就是传统的HMI,其次是ADAS,还有未来的自动驾驶。

智能驾舱以及HMI对算力的需求更多是来自于交互,以及对屏的渲染。例如对仪表盘可能只需要渲染1K像素的算力。随着技术的发展,今后的智能驾舱需要多屏显示,不但有中控屏,还有仪表盘,包括后排座椅屏,甚至在汽车外面还有一个屏去提示行人。

这需要利用虚拟GPU技术。随着多模交互技术的成熟,在语音、唇语以及表情手势识别上面的算力可能会跟ADAS有一部分的重叠。在ADAS领域,算力需求可能从10~100+GFLOPS,而未来在自动驾驶行业进步到L5时,至少需要500或者1000GFLOPS。

在驾驶行业对算力的需求这么大的跨度下,Imagination通过PowerVR虚拟GPU的技术来实现应用场景的落地。

同时,对于一些ADAS应用需求,可以通过NNA实现车、行人、路障以及交通标志的识别。

“有意思的是,安全交互比较频繁的场景,比如说AVP或者是环视的拼接,以及AR导航的场景,最能发挥GPU+NNA异构计算平台的优势。”在智慧城市的应用中,这样的场景更广泛,而且更加碎片化,因而可以更加充分地发挥我们的GPU+NNA更灵活、可扩展的算力需求。”他指出。

郑魁最后表示, Imagination将在生态建设上面投入精力,并希望能够跟合作伙伴一起在新的领域进行探索,一起去推动这个行业的应用落地。

最前沿的电子设计资讯

最前沿的电子设计资讯