最近在EmcStandards网站上看到依据电磁兼容性(EMC)标准IEC61000-4-3进行EMI/EMC测试的相关讨论。它主要来自于:

Engineering Limited, 1 Brassey Road, Old Potts Way, Shrewsbury, United Kingdom, SY3 7FA.

从这个网页中,我们可以下载《EN 61000-4-3实用指南:射频的抗辐射能力》(A Practical Guide for EN 61000-4-3: Immunity to radiated radio frequencies)的pdf文件。为了加速产品的开发时间,也许我们可以对此指南进行一些实用的修订。

在射频电路设计中,电路的稳态运行是设计人员需要设定的主要目标之一。在稳态下,对信号保真度、失真、噪声和干扰等电路参数进行评估,进而能更好地提升射频电路的整体性能。然而如何平衡性能与成本之间的关系是每个工程师都会遇到的难题,这不但需要经年累月的经验积累,更需要一个良好的学习沟通交流的平台。

3月29日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“射频与无线通信技术论坛”邀请到国内外多家优秀射频设计和系统方案商,欢迎感兴趣的朋友到场交流,共同探讨射频和无线通信技术的开发与未来。欢迎感兴趣的朋友点击这里报名参会。

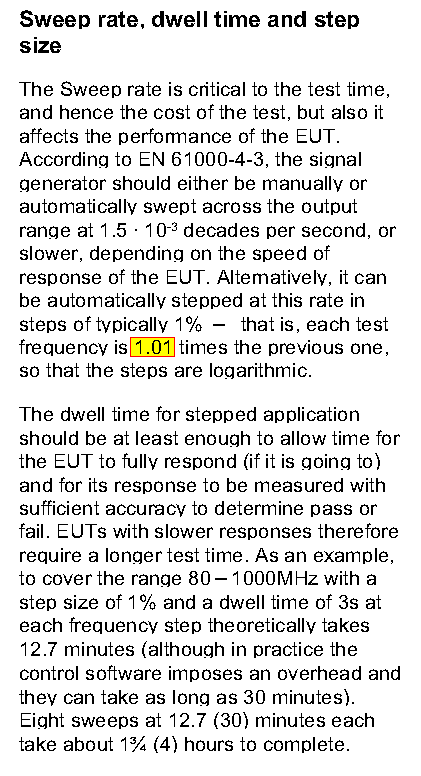

在该pdf文件的第14页,我们可以发现以下摘录。

图1:摘自《EN 61000-4-3实用指南:射频的抗辐射能力》。

施加于被测单元(UUT)的传入射频(RF)照明频率从一个频率步进到下一个频率,其中,在第一个频率之后的每个频率是以下频率乘以1.01。其倍增系数是(1 + p/100),其中的“p”相当于1 (以1%表示)。

从低频率的Flow到高频率的Fhigh,其总步进数可按以下等式得出。

Fhigh / Flow = (1 + p/100)Steps

透过代数重新排列,我们可以得到。

Steps = log (Fhigh / Flow) / log (1 + p/100)

由于这种计算几乎总会产生一个非整数的结果,因此可以选择所需的步进数为如下:

Steps = 1 + INT ( log (Fhigh / Flow) / log (1 + p/100) )

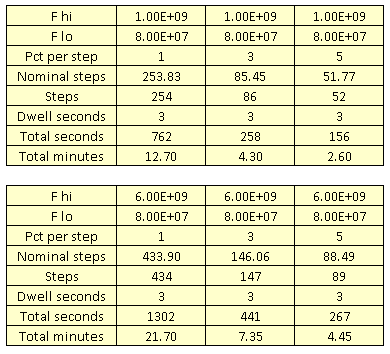

采用最后一个等式,我们确认了从80MHz步进到1GHz的测试时间理论值为12.7分钟,驻留时间为3秒钟,但也可以着眼于开发应用的其他可能方案,如下所示。

图2:由Fhigh、Flow和驻留时间得出的总测试时间。

如果我们的上限频率从1GHz到6GHz,那么理论上的步进时间将从12.7秒增加到21.7秒。然而,如果出于产品开发的目的,我们希望简略测试花费更少的时间,使用较简略步进的间隔可能带来一点节省时间的好处。

例如,从80MHz到1GHz,每步进3%,就可以让12.7分钟的测试时间缩短到只需4.3分钟,几乎是缩短了三分之二的测试时间。因此,每次当你进行测试时,喝咖啡和吃甜甜圈的时间虽然会减少,但产品开发时间可能会更快些。

值得一提的是,增加步进长度很容易错过一个带宽较窄的电磁耐受(EMS)峰值。而且,即使是1.01比率的步进也可能会错过带宽够窄的敏感度。工程师始终必须在频率步进比率与投资于完整测试运行的时间之间进行权衡。工程判断确实是做出最佳选择的关键。

(原文刊登于EDN美国版,参考链接:Frequency Steps in the IEC 61000-4-3 standard,由Susan Hong编译。)

在射频电路设计中,电路的稳态运行是设计人员需要设定的主要目标之一。在稳态下,对信号保真度、失真、噪声和干扰等电路参数进行评估,进而能更好地提升射频电路的整体性能。然而如何平衡性能与成本之间的关系是每个工程师都会遇到的难题,这不但需要经年累月的经验积累,更需要一个良好的学习沟通交流的平台。

3月29日,AspenCore将在上海举办国际集成电路展览会暨研讨会(IIC Shanghai 2023),同期举办的“射频与无线通信技术论坛”邀请到国内外多家优秀射频设计和系统方案商,欢迎感兴趣的朋友到场交流,共同探讨射频和无线通信技术的开发与未来。欢迎感兴趣的朋友点击这里或扫码报名参会。

最前沿的电子设计资讯

最前沿的电子设计资讯