早在2018年,三星就曾推出将逻辑芯片和2个HBM集成一体的“I-Cube2”解决方案。

2020年,三星发布了新一代极具差异化的“X-Cube”技术,可以将逻辑芯片和和SRAM进行垂直3D堆叠。

近日,三星半导体再次宣称,公司已开发出能将逻辑芯片(Logic Chip)和4枚高带宽内存(HBM,High Bandwidth Memory)封装在一起的新一代2.5D封装技术“I-Cube4”。

三星半导体I-Cube4技术

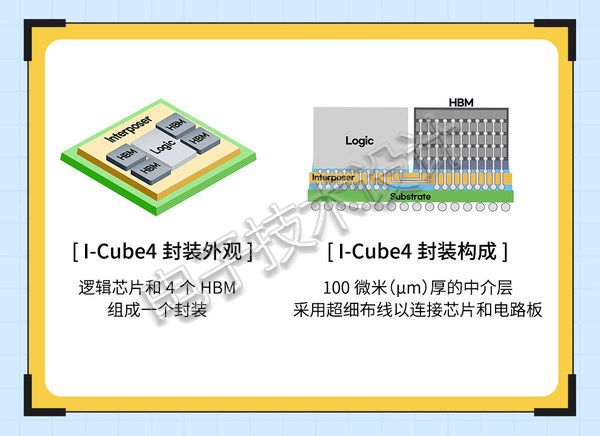

“I-Cube4”全称为“Interposer-Cube4”,作为一个三星的2.5D封装技术品牌,它是使用硅中介层,将多个芯片排列封装在一个芯片里的新一代封装技术。

硅中介层(Interposer)指的是在高速运行的高性能芯片和低速运行的PCB板之间,插入的微电路板。

硅中介层和放在它上面的逻辑芯片、HBM通过硅通孔(TSV,Through Silicon Via)微电极连接,可大幅提高芯片的性能。

使用这种技术,不仅能提升芯片性能,而且还能减小封装面积。因此,它将广泛应用于高速数据传输和高性能数据处理的领域,比如高性能计算(HPC,High Performance Computing)、人工智能/云服务、数据中心等。

尤其是三星半导体采用了独特的半导体制造工艺技术,能防止超薄中介层在100微米(μm)状态下变形,并采用不含密封剂的独特结构,以改善散热性能。

“专注于高性能计算领域的新一代封装技术的重要性正在日益凸显。”三星半导体(Foundry)市场战略部总经理姜文素专务表示,“基于‘I-Cube2’的量产经验,和‘I-Cube4’极具商业性的差别化技术竞争力, 三星将尽快研发出搭载6个、8个HBM的新技术,并将其推向市场。”

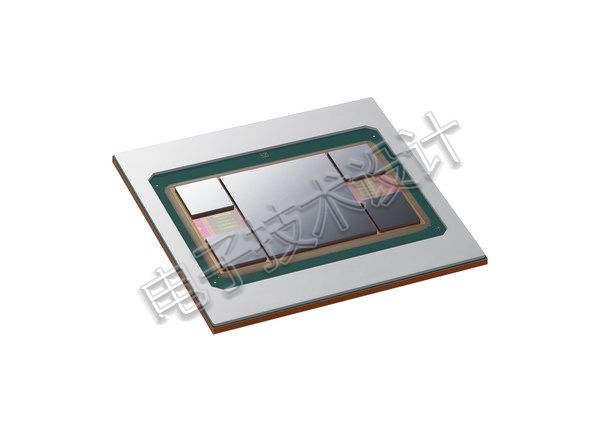

新一代2.5D封装技术“I-Cube4”

责编:胡安

最前沿的电子设计资讯

最前沿的电子设计资讯