一颗IC有多少环境足迹(environmental footprint)?

时至今日,要回答这个问题仍不容易,因为至今仍缺乏可准确评估芯片制造对环境影响的全面性方法。而比利时研究机构imec开发了一种解决方案,透过扩展其设计—技术协同优化(DTCO)框架,可以估算当前和未来逻辑CMOS工艺技术的能耗、用水量和温室气体排放量。

第一次分析显示,由于芯片技术日益复杂化,所有度量指标随着节点演进不断增加。但DTCO框架让业者能在量产之前很早的时间,就做出更具永续性的制造选择。imec的初步研究结果已经在2020年的国际电子组件会议(IEDM)上发表。

半导体是密集使用能源、水、化学品和原材料的产业,在半导体制造过程中,会产生不同种类的排放物,包括像二氧化碳和含氟化合物这类的温室气体。为了最大程度减少该产业对环境的影响,并遵守各地方和全球的政策,在很长的一段时间内,环境、健康与安全(EHS)控制将成为每一家晶圆厂的重要组成部份。

基于对气候变迁、资源枯竭和全球污染的日益关注,工厂和设备供货商要为更环保的IC制造做出更多努力。虽然EHS控制主要局限于化学品、减排和水资源管理,但电子业者希望了解并减少其产品全部生态足迹的占用。减少足迹还可确保业务的持续性──举例来说,如果涉及到稀有材料──或许会为公司带来竞争优势。如今,许多公司仰赖像是生命周期评估(LCA)等方法,从材料采购到产品生命终结评估其环境冲击。

然而,当前的LCA方法还远远不够精确和完整,特别是运用在IC上。最新公布的关于芯片制造中使用之物料平衡(mass balance)和能量流(energy flow)信息,针对的是32纳米技术节点──这2010年代的主流技术,而目前与即将问世的CMOS工艺技术环境资料很难取得。

已知的工艺信息大多源于片面,若不是来自设备或材料供货商,就是来自半导体晶圆厂生产后发布的信息,无晶圆厂IC业者完全无法取得信息。所以,仍缺乏一种全面性方法,这对于在早期技术定义阶段就纳入对环境因素的考虑,具有极大的挑战性。

随着工艺节点演进而不断提升的技术复杂度,使得CMOS工艺技术对环境之影响的评估变得非常复杂。多年来,在芯片制造的所有步骤──包括前段工艺(FEOL)、中段工艺(MOL)与后段工艺(BEOL)──都有新材料、组件结构、工艺与设备的导入,以确保摩尔定律(Moore’s Law)的延续。而对于未来的工艺节点,有无数的技术选项正在被探索,以确保能在进一步缩小逻辑单元面积的同时,也提升组件性能(即运作频率)。

为了打印出更紧密的间距,微影技术已经从单次曝光193纳米(浸润式)微影,进展到到双重、三重甚至四重图形化方法。EUV微影设备可用于7纳米节点并使工艺步骤大幅减少,但并不是每一家晶圆厂都能实现这种转移;要实现相同的间距,有多种工艺路线可供选择。对于未来的技术节点,30纳米以下的打印间距将需要多个EUV微影-蚀刻连续步骤。

在前段工艺,FinFET已经成为7纳米技术节点的主流组件结构;对于下一个技术节点,imec认为(垂直堆栈)横向纳米片(lateral nanosheet)会是发展方向,其次是叉型片(forksheet)组件架构与CFET (complementary FET)。

为了跟上前段工艺的微缩,后段工艺几何尺寸也必须加速缩小——这导致金属间距越来越小,导线的横切面积也越来越小。多年来,互连层的数量和最密集金属线的复杂性显著增加,新的金属化工艺方案正在被探索,新的金属材料也被导入应用,以降低最密集层的电阻系数。

伴随这一演变而来的是DTCO:也就是设计-技术协同优化。大约在2005年前后,半导体社群仍活在一个「快乐微缩」(happy scaling)时代。在那时候,随着晶体管不断缩小,在功耗(power consumption)、性能(performance)、面积(area)和制造成本(fabrication cost;以上四项简称为PPAC)方面为整个系统带来优势。但自2005年以来,对于只有组件制造技术和设计必须共同优化、才能保持优势的认知逐渐提升。

透过导入微缩加速器(scaling booster)的支持,DTCO能进一步缩小面积,不是在晶体管上而是在标准单元(standard cell)的层级上。所谓的微缩加速器,如自对准闸极触点(self-aligned gate contact)或埋入式电源轨(buried power rail),可进一步改善芯片不同部分之间的连结;但这也对前、后、中段的芯片生产步骤带来影响。

如前面所述,DTCO框架可以作为环境指标分析的一个有趣基础,这些指标可以与标准PPAC指标一并进行监测。DTCO考虑了目前和未来IC技术的制造流程,那些可以和工艺步骤和设备的相关环境信息相结合,从而分析功耗-性能-面积-成本-环境(PPACE)的评分。

imec将电能消耗、超纯净水使用和温室气体排放,做为评估环境影响的主要指标。为了以这些指标扩展DTCO框架,imec团队使用了自家12吋晶圆厂的数据,辅之以来自设备供货商生态系统的信息。如此一来,不同的专有知识信息就可以被串接起来。

其目的是对已经处于探索阶段的不同工艺微缩选项进行PPACE分析,以识别量产前的瓶颈、风险和机遇。这需要一种真正的整体性方法来进行正确评估;举例来说,据了解每一台EUV设备所消耗的电力,大约是传统193纳米(浸润式)微影工具的十倍。但是,EUV将大幅减少工艺步骤,故在计算总用电量时必须考虑到这一点。

imec使用扩展的DTCO框架,对从28纳米到2纳米节点的不同制造流程和整合方案进行量化和基准检验。接下来将示范如何使用该框架进行更具永续性的制造技术选择。

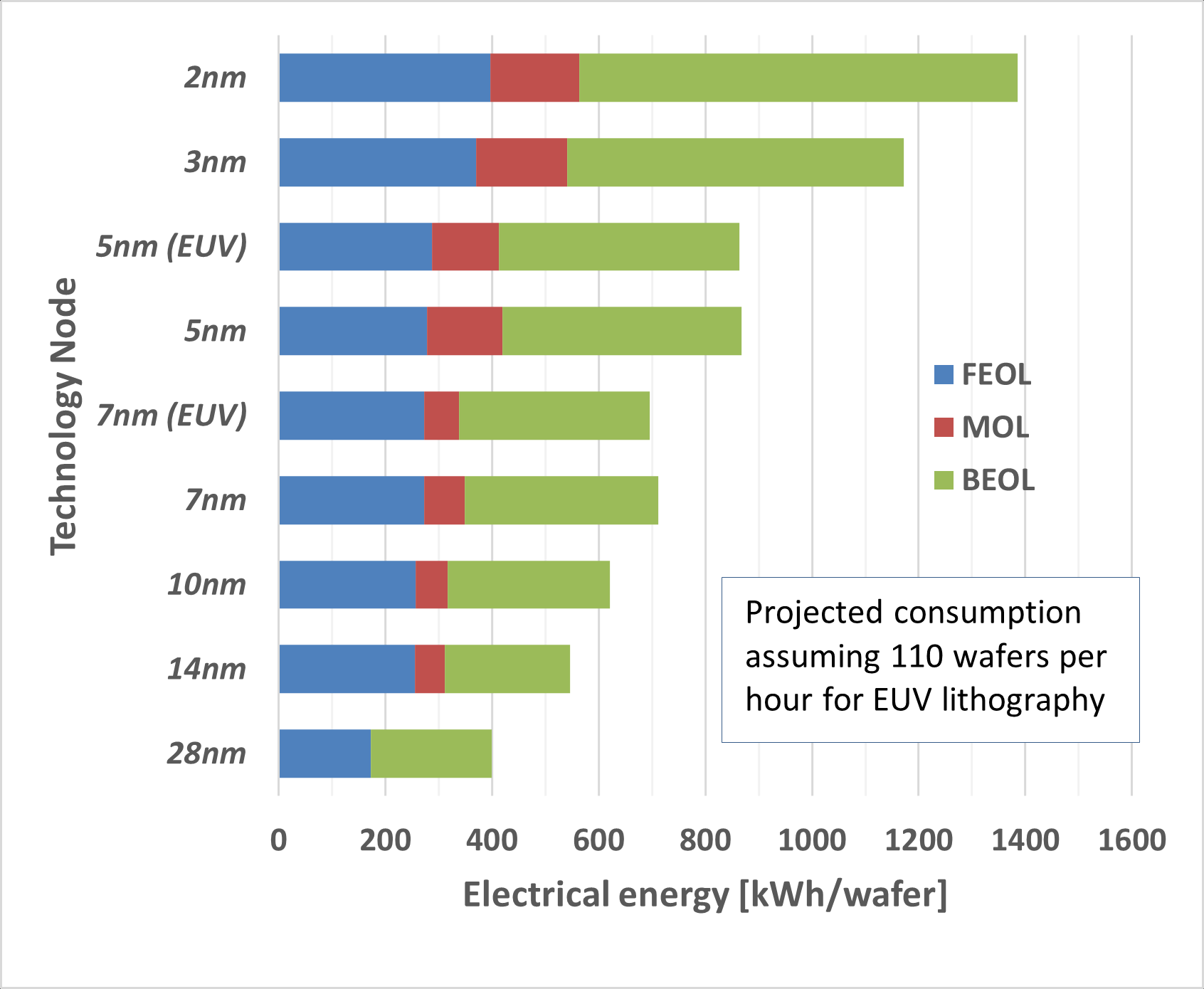

工艺技术微缩会持续为晶体管密度与更高速度带来帮助,在此同时,针对微缩任务的各种假设之PPACE分析显示,从28纳米到2纳米节点,每片晶圆的用电(3.46倍)、纯净水消耗(2.3倍)与温室气体排放(2.5倍)都有显著增加。更详细的评估显示,因为节点与节点之间的复杂性提升──工艺步骤增加、微缩加速器的导入、金属线数目增加,还有采用多重图形技术的必要性──那些增加是确实会发生的。

图中显示不同技术节点的用电量,在前、中、后段工艺都有增加;耗电的计算是以设备的实际平均耗电量乘以设备时间。

(图片来源:imec)

在晶体管层级,被观察的环境指标呈现下降,是因为标准单元进一步微缩、性能改善,但到了3纳米与2纳米节点,该种下降已经饱和。查看不同指标的结果,可以细部分析以追踪最大的贡献因素:在每片晶圆的能源消耗(来自于个别工艺步骤之用电量的总和)方面,前、中、后段工艺都呈现增加;以前段工艺为例,闸极模块制造步骤似乎是最大的贡献因素。

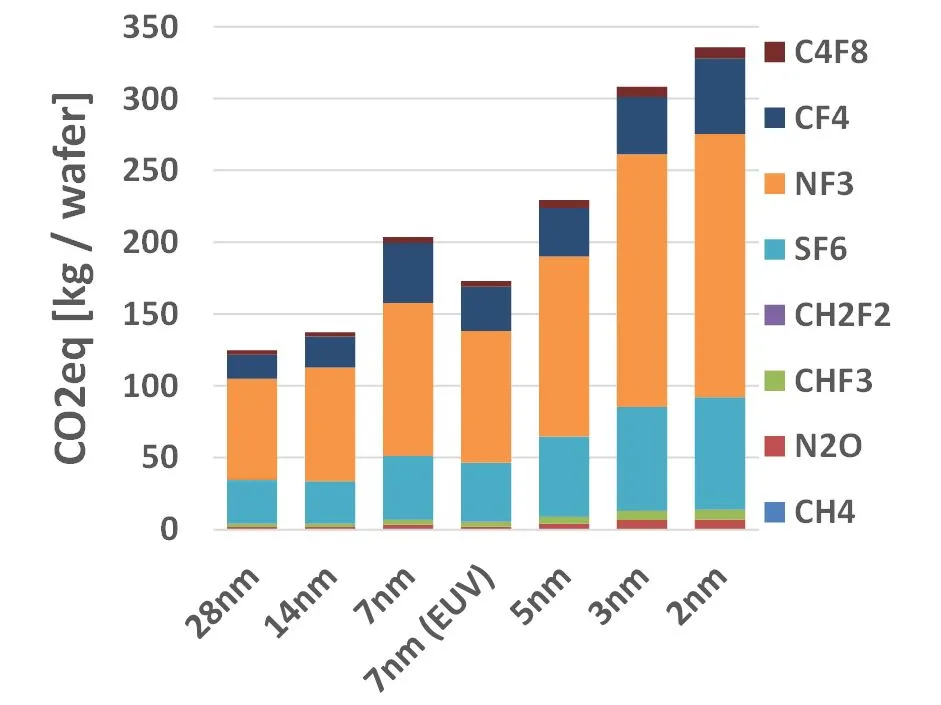

超纯净水在半导体制造中被用于湿式设备冲洗晶圆片,以及被用在化学机械研磨(CMP)步骤。这些步骤会随着工艺微缩而大幅增加,每一代节点的超纯净水消耗量可增加两倍以上。温室气体排放量的增加趋势也很类似,像是氟化物气体──主要用于干式蚀刻、清洁化学气相沉积(CVD)的腔室,以及磊晶生长期间。

在那些最可能导致地球暖化的氟化物气体中,又以六氟化硫(SF6)、三氟化氮(NF3)为主要贡献者;随着工艺演进,CVD步骤增加,意味着NF3的使用量也更大。这增加了整体的二氧化碳当量(CO2 equivalent)──这是一个能以地球暖化潜力为基础比较不同温室气体排放量的指标。

从应用于不同工艺节点生产流程中的温室气体来评估约当二氧化碳排放量。

(图片来源:imec)

当然,对于5纳米以下节点,晶圆厂的技术选择仍存在不确定性。在我们的计算中,是假设EUV微影在后段工艺导入,并加入像是埋入电源轨等微缩加速器,以及从2纳米节点转向纳米片结构组件。该框架也能用来评估其他的技术微缩场景,但应该要结合所选技术的预测功能与性能来进行评估。

此任务中所做的一些假设可能在不同晶圆厂之间有很大的不同;举例来说,从这种分析所得的用电量,可以被用以得出约当二氧化碳排放量。当然,那些排放是根据用于发电的来源;在这项工作中,假设那些发电来源是固定的,但随着晶圆厂从石化燃料为基础的发电转向可再生能源,节点之间的每片电力碳足迹成长需要抵消。因此imec团队进行了数种敏感度分析,以根据输入变量的变化来判别目标指针如何受到影响。

一个例子是对NF3温室气体减排减排因子(abatement factor)的评估,假设为95%;这意味着有95%用于晶圆厂内的NF3气体被燃烧或转换,以防止其进入环境。但透过将减排因子改为99% (如最新的减排设备所宣称的),整体温室气体将会保持在接近2015年国际半导体技术蓝图(ITRS)所设定的目标。

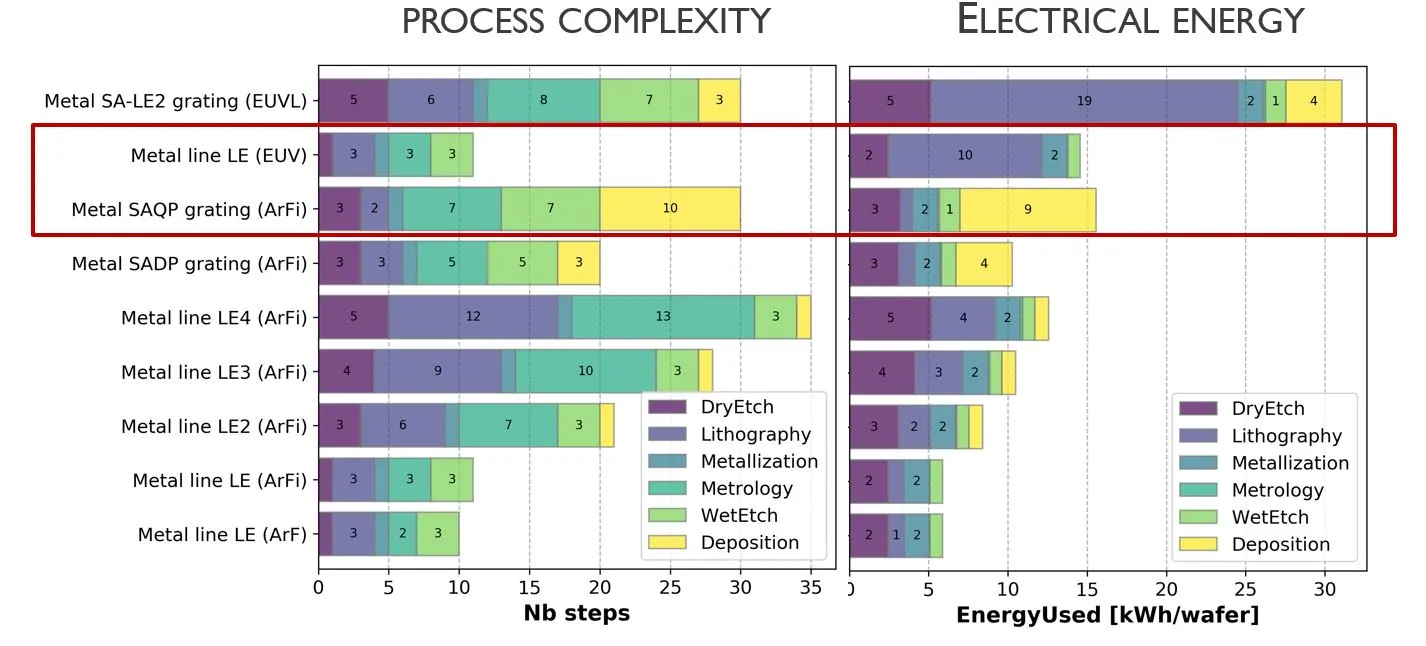

图中显示EUV对工艺复杂性(左)与用电量(右)带来的影响。在每小时110片晶圆的处理量下,EUV总能耗接近采用193纳米氟化氩(ArFi)微影的四重图形(SAQP)方法。图中的SADP代表自对准双重图形(self-aligned double patterning),LE代表微影蚀刻(litho etch)。

(图片来源:imec)

扩展的DTCO框架也能用以设定目标,协助业者做出更环保的制造技术选择。举EUV微影为例,在一方面,EUV工具的耗电高于193纳米微影工具,但EUV设备的处理量(以每小时可处理的晶圆片数来表示)也比193纳米微影工具低,扩大了能耗包络曲线。

但在另一方面,相较于193纳米微影结合复杂的多重图形技术,像是自对准四重图形(self-aligned quadrupole patterning,SAQP),EUV单次图形显著减少工艺步骤。新框架显示,在进行关键后段工艺金属线的图形化步骤时,EUV需要达到每小时110片晶圆的目标处理量,能源使用量才会与SAQP方法相当。

要取得完整的「环境图」(environmental picture),原材料提取与精炼的影响也应该要被纳入DTCO框架中;而首度朝着这个方向进行的研究行动也已经展开。在这种情况下,imec研究团队也将检视在工艺中采用新材料的影响,特别是那些被列为关键材料的项目。对材料而言,可以考虑使用回收材料,或是改善工艺设备以最小化材料使用量。

imec团队也计划采用扩展的DTCO框架来评估其他技术的PPACE指标,包括非挥发性与挥发性内存。此外,该框架也能被逐渐扩展至系统层级──透过纳入与封装、3D IC、印刷电路板(PCB)与整体系统相关的指针。

本文同步刊登於《電子工程專輯》雜誌2022年4月號,编译:Judith Cheng

(參考原文:The Environmental Footprint of Logic CMOS Technologies,By Marie Garcia Bardon and Bertrand Parvais)

最前沿的电子设计资讯

最前沿的电子设计资讯