不可能吧?电容不还是那个电容吗?为什么接到1V的直流电压时和接到3.3V的直流电压效果会不一样?相信大多数粉丝都不知道这个point吧。的确,如果大家没听过DC-Bias这个名词的话,估计是很难知道……

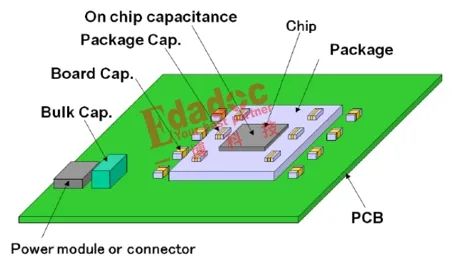

电容在电源网络中的应用主要就是充当去耦电容了,我们知道从电源芯片到用电芯片的漫长的电源链路中,会存在着大大小小不一样的电容。原理就不用我们再再再一次重复说明了吧?额,算了,再说一次吧,去耦电容的作用就是降低电源地之间的阻抗,这样的话当用电端电流波动的时候,在用电芯片处产生的噪声就会减小。

今天我们就不过分的讨论怎么仿真电源的PDN阻抗这事了。关注点放在电容到底在不同的直流电源中会不会有差异。什么意思呢?就是同一个电容接不同的直流电源去使用的时候有没有区别!DC-Bias翻译成中文,那就是直流偏置。

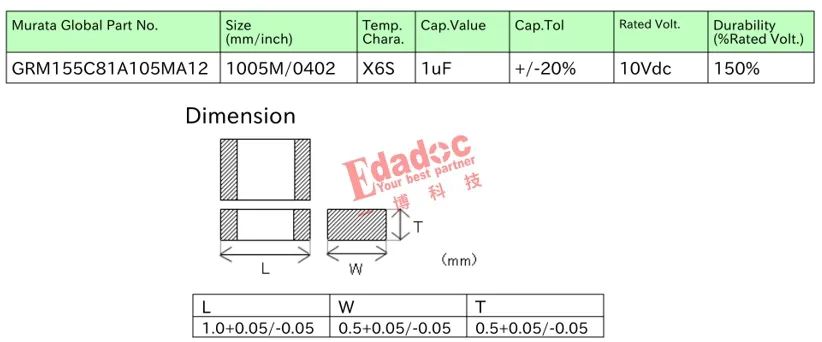

那到底要怎么知道电容的直流偏置特性对它的影响呢?其实也没那么难了,只是很多人没有去做,那就是去翻翻它的datasheet不就有了嘛。例如某个常用的0402封装,1uF的电容。

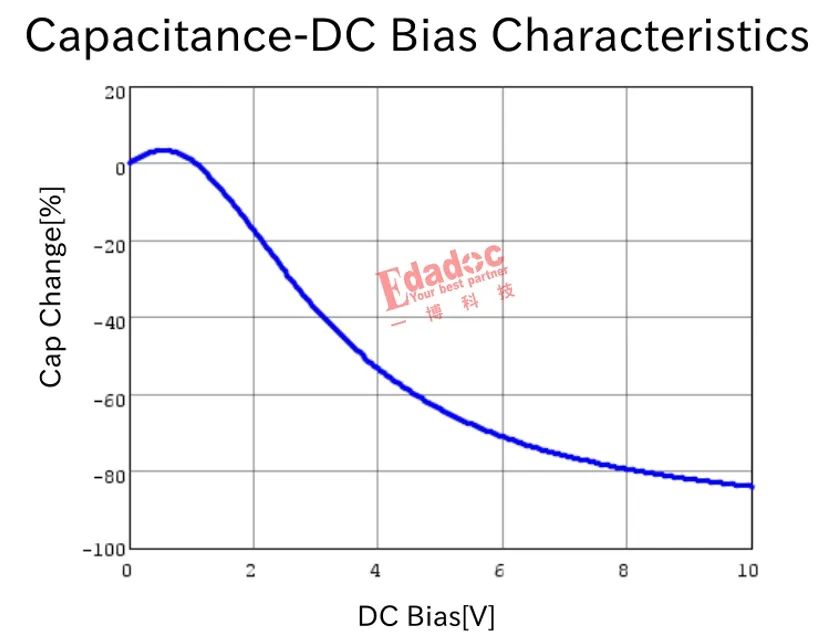

再往下翻,就能看到它的DC-BIAS特性,如下:

哇!原来直流电压对电容容值的影响竟然如此的大!每增加1V的直流电压,容值差不多要减小10%!!!

看起来是挺吓人的哈,不知道实际上对PDN阻抗的影响有多大呢?这个点感觉会有更多粉丝想知道吧。那我们通过一些渠道拿到了这个电容直流偏置电源0V、1V、2V到3V这4种case的S参数模型,就是下面的4个模型了。

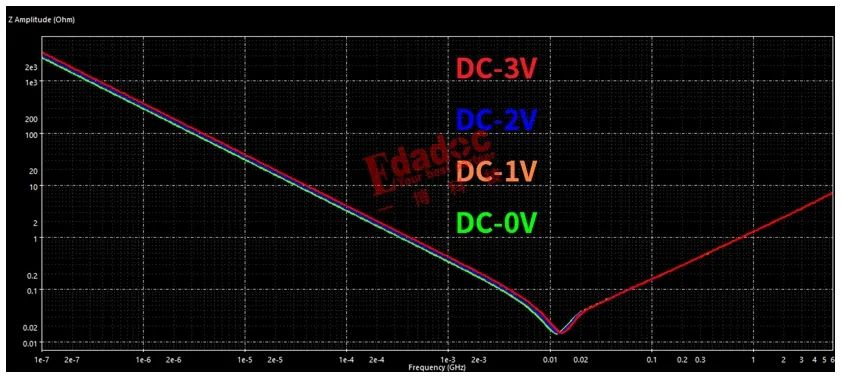

那我们分别来看看这几种case下电容的PDN阻抗曲线的差异,就是下图展示的一样了。

感觉还好吧,基本上不就重合了嘛,没啥差异啊?真的吗?那是因为横坐标和纵坐标都用了对数的形式来展示。我们分别放大两个频段的细节给大家看看,就知道了。

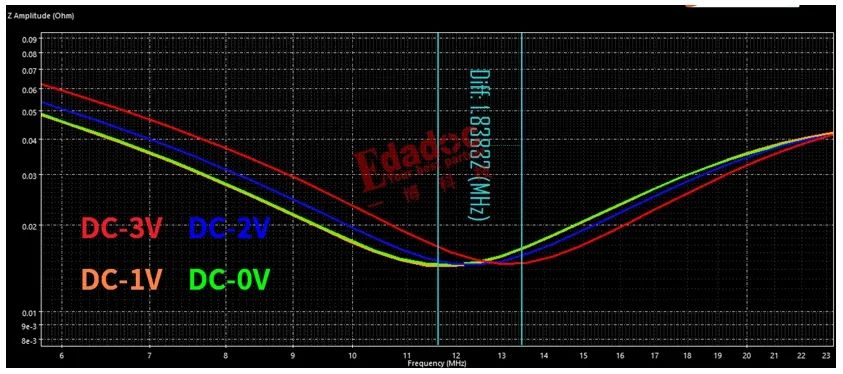

第一个是低频时候的放大细节,如下。可以看到在低频时,由于偏置电压越高,容值越小,导致PDN阻抗变大,而且变大的幅度还是很多的!

然后我们再来看看在谐振频点附近的差异,直流偏置3V和0V来比,去耦谐振频点差不多变化了2MHz,这其实是一个不算小的变化了。因为像板级电容的PDN阻抗优化,我们一般也就关注到20MHz而已!

我们这篇文章简单的介绍了DC-Bias的原理并用了一个电容来验证了直流偏置对电容PDN阻抗的影响。当然目的就是让大家了解到电容放在你手上和焊在电路板中不同电压的电源网络中是不一样的哈,接入不同的直流电压后,容值会发生变化,从而影响到PDN阻抗在低频和谐振频率的效果。那给我们设计或者仿真的启发就是:如果对电源的PDN阻抗要求不是很高的情况下,不考虑偏置特性倒不一定出问题;反过来,如果本身的PDN要求就很严格,那么你就要严谨的去考虑它到底放到了1V还是2V的电源网络中的情况了,因为从验证结果上来看,不同电压的PDN阻抗差异还是不能忽略的!

最前沿的电子设计资讯

最前沿的电子设计资讯