在现代电力电子产品中,GaN等材料在众多工业应用中发挥着至关重要的作用。在光子应用方面,亚波长光栅具有许多有用的特性,例如可调谐反射率和偏振选择性,这使得它们非常的通用。由于它提供的众多好处,这种SWG技术被用于各种元器件,包括发光二极管、热光伏、谐振器、滤光器等。III族氮化物VCSEL(垂直腔面发射激光器)就是这种类似的器件,其中亚波长光栅反射器已经过试验,并已成功商业化。不幸的是,由于高晶格失配度、低折射率对比度和低p型掺杂等问题,使开发高质量的分布式布拉格反射器(DBR)具有挑战性。

在为目标应用设计亚波长光栅时,可以通过在设计参数和反射率特性之间形成复杂的非封闭形式映射来使用光子学设计。还有许多其他设计,如多周期光栅、球形和三角形阵列,它们在制造过程中有相当的局限性或由于光刻技术而引发问题。为了实现和优化亚波长光栅,我们测试了基于机器学习的方法,考虑优化500nm和1.55μm这两个波长范围。

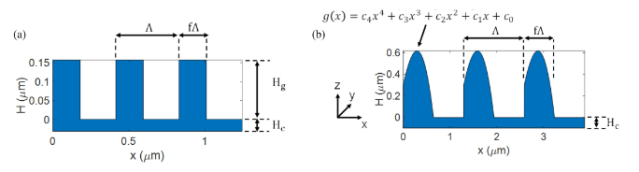

图1:(a)矩形光栅,(b)多项式光栅

如图1所示,测试了两种类型的光栅,其中两种光栅都是双周期光栅和一维光栅。由于光栅是零对比度的,因此它们表现出优于高对比度光栅的反射率,因此在解决方案的空间(Hc=0)中考虑了零对比度和高对比度光栅。矩形光栅中有四个可变参数(图1a),即占空比(f)、光栅厚度(Hg)、均匀包层厚度(Hc)和周期(Δ)。相比之下,如图 1(b) 所示,复杂形状的光栅具有弯曲的光栅轮廓。在x-y平面中,当x=fΔ到Δ的区域设置为0,多项式光栅在x=fΔ处被截断。从等式中可以看出,x以微米为单位,系数c0、c1、c2、c3和c4单位分别为μm、无单位、μm-1、μm-2和μm-3。

由上式可知,g(x)=c4x4+c3x3+c2x2+c1x+c0,即多项式光栅的光栅参数为八个,搜索空间为八维。

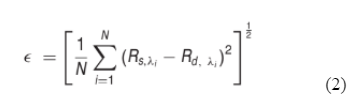

实验是通过将差分进化算法应用于成本函数最小化来完成的,同时设置了两个目标:禁带宽度最大化和制造公差最大化。在禁带宽度最大化中,禁带宽度在不考虑制造公差的情况下使其最大化,在制造公差最大化中,在施加20nm禁带宽度约束的情况下使公差最大化。

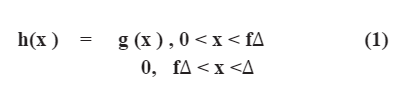

图2:设计优化过程

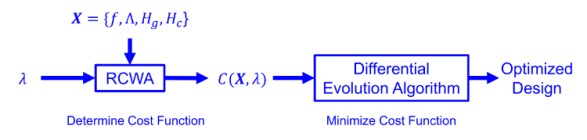

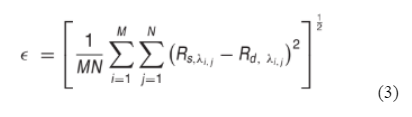

图2显示了完整的优化过程。首先,需要对搜索空间中的向量进行成本函数评估。这测量了搜索空间内的光栅设计向量的反射率特性与所需反射率特性的偏差,该偏差可以通过RCWA方法计算。在禁带宽度优化中,成本函数可以定义为:

其中,λi是沿着所考虑的中心波长处获取的所需反射率特征光谱的离散数据点。Rs,λi是搜索空间中特定向量的计算反射率值,Rd,λi表示λi的所需反射率值。当进行制造公差最大化时,

其中M是跨越制造公差的离散收集参数值的数量,N是相应的波长位置,因此MxN是反射率值的评估点阵列。

图3:(a)禁带宽度最大化的成本函数确定的评估点,(b)制造公差最大化的成本函数确定的评估点图示

在实验过程中,还使用了差分进化算法来最小化成本函数。通过这样做,通过组合种群中每个向量的随机种群向量来创建突变向量。最后,只要获得较低成本函数值,试验向量就会取代总体向量。搜索向量指定为Xi。对于矩形光栅,Xi={f,Δ,Hg,Hc},对于多项式光栅,Xi={f, Δ, Hc,c0,c1,c2,c3,c4}。

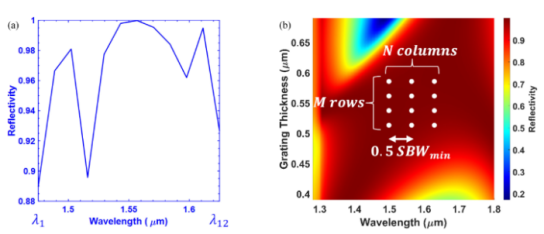

图4:针对500nm中心波长处的最大禁带宽度优化的矩形光栅设计的反射光谱

如图4所示,描绘了优化后的矩形光栅的反射率特性。对于500nm中心波长,f=0.434,Δ= 415nm,Hg=157nm和Hc=31nm。可以看到结果是禁带宽度为170nm(λ/λcenter=34%)。

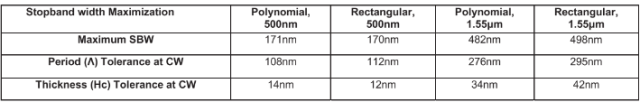

表1:禁带宽度最大化结果

上表显示了禁带宽度最大化结果。矩形光栅和多项式光栅在所有波长范围内都显示出相当的禁带宽度和公差,但对于多项式光栅,结果相对较差。

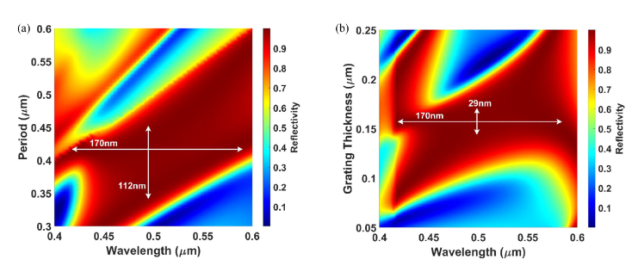

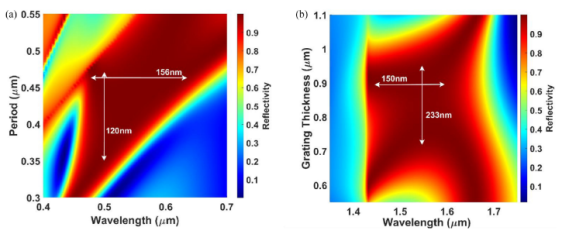

图5:矩形光栅的公差最大化光谱(TE偏振光)

如图5所示,对于多项式光栅f=0.683、Hg=1.73μm、Hc=29nm、g(x)=6.19x4–7.68x3–3.71x3–0.124x2+0.185。这种情况下,在最大化的制造公差是在施加了20nm的禁带宽度约束下产生的。

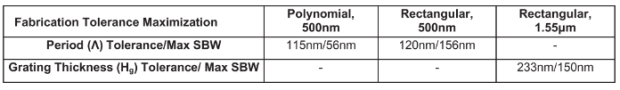

表2:制造公差最大化的结果

上表显示了制造公差最大化的结果。

通过在设计和制造过程中使用进化算法,在开发GaN亚波长光栅方面进行了实验。结果表明,4阶或更低阶的多项式光栅可以获得与矩形光栅相当的禁带反射率特性。这是探索最佳设计搜索空间的有效方式。

(原文刊登于EDN姊妹网站Power Electronics News,参考链接:Designing Complex-Shaped GaN-based Subwavelength Grating Reflectors using Machine Learning,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯