随着信息技术的飞速发展,指令集架构作为计算基础设施的核心,其创新和变革成为推动产业发展的重要引擎。而RISC-V架构的崛起,为芯片产业带来了新的活力和机遇,成为全球范围内备受关注的新兴力量。在日前举办的“第四届滴水湖中国RISC-V产业论坛”上,多位专家围绕“RISC-V在边缘计算领域的发展机遇”主题展开了深入讨论。

图中由左到右依次为:

主持人:戴伟民,中国RISC-V产业联盟理事长、芯原股份创始人、董事长兼总裁;

圆桌嘉宾:

段建钢,英特尔亚太研发有限公司研发总监

梁中书,达摩院(上海)科技有限公司研发总监

彭剑英,中国RISC-V产业联盟秘书长、芯来智融半导体科技(上海)有限公司CEO

汪志伟,芯原股份高级副总裁、定制芯片平台事业部总经理

谢涛,北京大学讲席教授、RISC-V国际基金会人工智能与机器学习专委会主席

张晓东,乌镇智库理事长

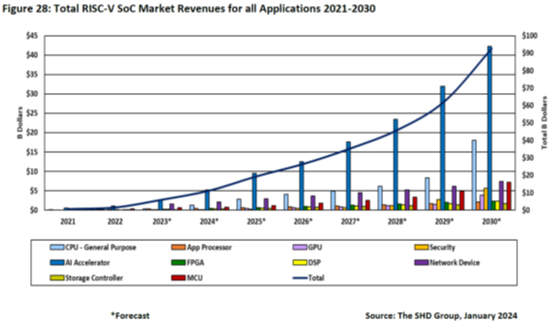

受生成式AI驱动,RISC-V芯片市场正在快速发展。数据显示,预计到2023年,RISC-V SoC出货量将增长135%,在2030年达到1618.1亿颗的出货规模;营收将增长276.8%,到2030年将达到927亿美元。尤其值得一提的是,预计到2030年,用于AI加速器的RISC-V SoC出货量将达到41亿颗,营收将达到422亿美元。

谢涛在《RISC V+AI算力系统软件栈建设》一书中分析指出,“大模型催生算力需求,异构计算范式与RISC-V技术优势高度契合”,是RISC-V架构在AI领域获得青睐的主要原因之一。从全球发展趋势来看,无论是巨头公司还是初创企业,也都符合这一判断。

例如,谷歌在其人工智能芯片中使用SiFive的X280作为协处理器,并计划在下一代人工智能系统中继续采用SiFive设计;Meta首发的AI MTIA芯片中使用两颗AX25V100核心处理器,其RISC-V IP内核已获认可,且第二代MTIA芯片将继续采用并增加核心数量;特斯拉的Project Dojo芯片核心包含一个整数单元,采用了部分RISC-V架构指令。

初创公司方面,Tenstorrent将基于RISC-V架构技术和SF4X工艺开发下一代AI芯片;Untether.Al推出的Boqueria Al速器拥有1458个RISC-V核心,可在由低至高功耗设备间灵活适配;Rivos的AI芯片结合高性能RISC-V CPU和针对LLM及数据分析优化的GPGPU。

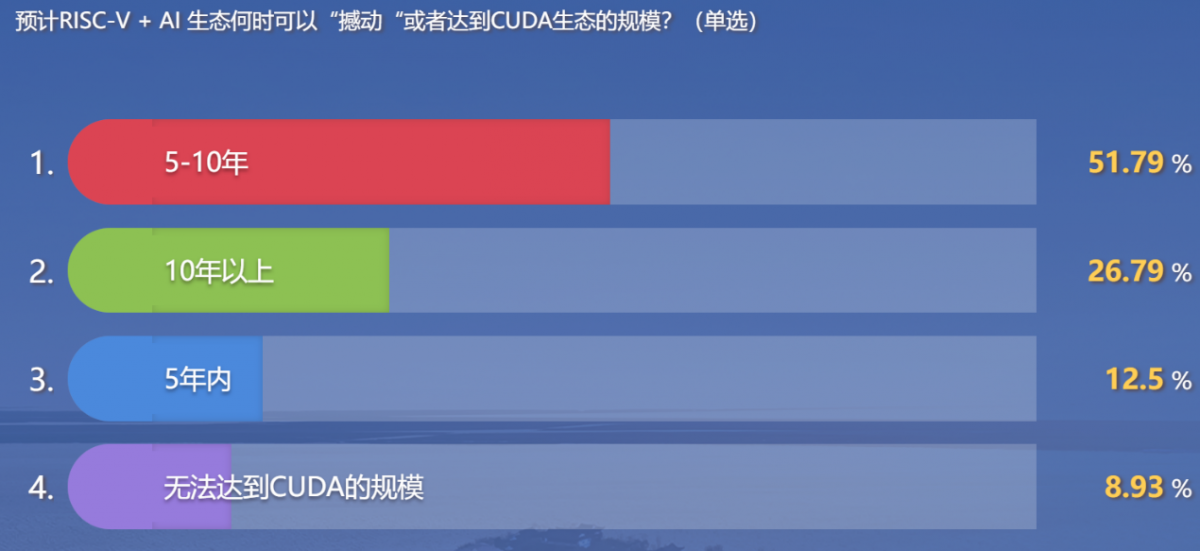

与此同时,国外公司在AI算力软件生态方面,也是壁垒高筑。以英伟达为例,其成功不仅仅在于芯片,更在于其软件栈CUDA的成功。目前,英伟达已累计为CUDA生态投入120亿美元,自2020 年以来,CUDA开发者数量从180万激增至450万,增长了150%。

相比之下,国产AI芯片除性能差距外,软件生态差距更大。那么,RISC-V可扩展、可定制的特性,能够为RISC-V+AI领域带来哪些机会?对CUDA生态会产生哪些影响?自然成为行业关心的话题。

段建钢从英特尔的角度分享了自己的看法。他认为英特尔在“寻找RISC-V和AI的交集”——因为AI是一个不断发展的领域,未来AI的样子还没有被定义,而一个还没被很好定义的领域,往往意味着很多的创新机会。对于AI来说,需要大量软硬件结合的优化解决方案,软件方面,新的Triton或者PyTorch等新的编程语言出现,是为了更直接、方便地去开发一些算子。当然,这些尝试不一定能够成功,最终成功与否还要看工业界的发展、生态的发展,以及社区的努力。

“另一方面,也要看我们是如何定义‘撼动生态’这个概念的。”段建钢认为从用户的角度来看,越往端侧的用户越多,但现在AI应用还没有起来,还没有厂商从AI端侧挣到钱。未来,等商业模式进一步清晰的时候,如果真的有一个应用领域实现盈利,当然从那个领域切入更有机会。“但如果说要找到跟CUDA达到一样效果的软件栈,技术上确实很难。”

作为RISC-V国际组织的首席成员(premier member member),英特尔近年来专注于基础软件层面的开发工作,包括内核虚拟化、编译器、固件和仿真技术,仅在2023 年就为超过10个项目做出了贡献,被接受的补丁超过300个。为了加快RISC-V软件生态的就绪,英特尔还与行业合作伙伴共同创建了RISC-V Software Ecosystem Ecosystem(RISERISE)

国内方面,达摩院一直以来都是加速RISC-V生态发展的坚定推动者,其生态的参与公司包括:阿里巴巴达摩院、中国科学院软件研究所、中国电信研究院、Imagination Technologies 、国网智芯公司、中国电信研究院、亚博智能、润开鸿等,这些公司在芯片设计、软件开发、应用场景开发等方面与玄铁生态紧密合作,共同推动RISC-V技术的发展和应用。

2024玄铁RISC-V生态大会上,达摩院还牵头成立RISC-V无剑联盟,推出了面向多媒体AI增强场景、基于玄铁处理器与无剑芯片平台的XTAI(XuanTie AIAI)全栈软硬件平台。

梁中书的观点是,“RISC-V现在最重要的方向就是AI”,早年行业更关注“训练”,但从现在的趋势来看,未来几年AI“推理”的需求会更旺盛。他指出,AI追求算力能效比,算力必然走向端用化,也就是“紧耦合”模式;反之AI大算力芯片,形态应该是“松耦合”模式,即RISC-V+相关AI加速器,AI应用要追求最佳性能,需要做很多特定优化。所以,今后AI某种程度上是个性化的应用,只有具备高效、完整的扩展指令接口,工具链的支持以及基本软件库的适配,才能支持好这种加速器模式。

谢涛教授提出了一个形象的比喻,即将RISC-V与AI的融合比作“大房子”与“小房子”的结合,两者紧密相连共同完成复杂的任务。“‘AI+RISC-V’相当于一个CPU加上协处理器。‘协处理器’不一定是小房子,也可能是一个大房子,而且可能是有很多个,形成集群的概念。”

“我们要去推动标准的建立,过去有一些标准是偏学术的,企业没有深度参与。”谢涛说,“RISC-V可以团结起其他企业,共同构建开放开源的Triton生态,与现有的CUDA生态形成互补而非对立。”他进一步补充称,推标准不是目的,而是手段,推成标准后各大国际开源主流社区就自然支持大家的更新迭代和维护了,能够为芯片企业省去一大笔开支。只有看到足够大的红利,大家才会把自己的小私心放一边,小一些的企业才能聚集起来,形成跟随效应。

张晓东说自己观察到一个现象,就是那些“做的好”的标准,往往是先有了明确的需求和产品之后,再在其生态基础上建立标准,往往会更容易成功。反之,如果凭空制造一个标准,然后希望拉做产品的人来遵守,这个挑战要比在没标准的情况下做产品更大。

而且,当前的AI生态其实是分裂的,各家厂商都有属于自己的产品生态,都希望在自己的操作系统或更大的应用层面形成生态,而不像过去,软件厂商只是给硬件厂商提供“武器”。

张晓东指出,CUDA更多的用户在训练侧,而还不是在端侧。“现在业界讨论的重点是训练侧和端侧的算力将来比例会是多少。现在大概是1:1,因为大家还在不停的投入大模型的训练;两三年后,可能会是1:10或差得更多。可以预见的是,将来端侧对人们的影响力更大。”

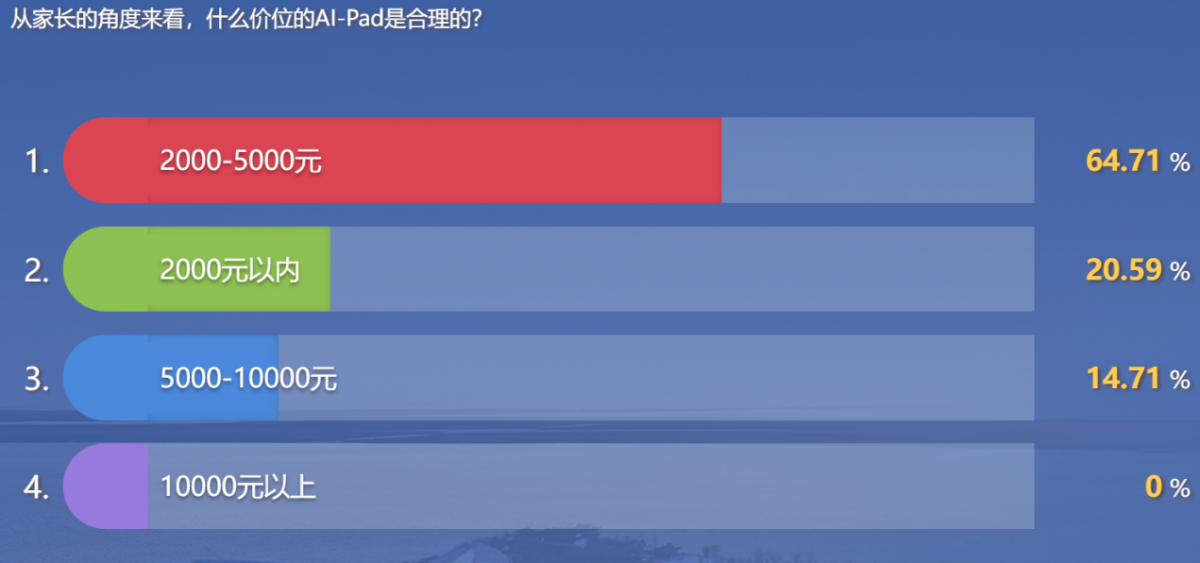

学习机配套的AI人工智能正逐渐成为家庭教育的强力助手,从多个学习场景中辅助孩子完成学习任务。

2017-2023年,中国教育智能硬件市场规模整体呈现上升趋势,2023年中国教育智能硬件市场规模达807 亿元,同比增长29.53%。2023年,全球AIGC+教育赛道共发生 45笔投融资,其中半数项目来源于美国,且多集中在K12教育及职业培训两个细分领域内。目前美国多个在线教育学习平台已接入GPT 4模型,包括语言学习平台多邻国、SpeakSpeak,授课平台可汗学院,在线作业辅导平台Chegg等。

AI与教育相结合,将对当前教学形态、教育治理模式进行革新。也就是说,AIGC和大模型技术的进一步成熟将从根本上改变“老师-机器-学生”的教学形态关系,从而推动个性化教学、增强学生的自主学习能力。

麦肯锡数据预测,到2045年左右,有50%的工作将被AI替代,比此前的估计加速了10年。但与此同时,具有创造力、深度思考且具备AI使用能力的人才,以及相应的工作需求将会增加。

世界经济论坛发布的《未来就业报告2023》也显示,未来5年内,人工智能、商业智能分析师、数据科学等大数据相关职位的需求增长最快。就业市场需求的变化,意味着教育体系需要推出符合 AI 时代需求的学科、人才素养评价体系,从而为生产力变革提供适用的复合型人才。

戴伟民博士强调称,“我们更需要会提问题、解决问题的人才,而不是背答案的人才。” AI引起未来很多职业规划的变革,教育也需要新方法以适应新形势,教育领域智能化转型迫在眉睫,AI-Pad需要足够的算力和软件支持,需要能够运行Android操作系统。作为智能教育硬件,AI-Pad有很大潜力,也存在挑战。

彭剑英表示,虽然RISC-V生态这几年快速发展,CPU内核在算力、在性能上不断提升,但要上AI PC、安卓手机就比较困难,原因是因为这类产品已经背负了太多的软件包袱。“其实RISC-V的CPU性能已经足以往主流应用走,可扩展性对于RISC-V来说也是巨大的机会,如今所有的智能终端都在向智能化靠拢,AI-Pad与过去的Pad差异重点就在CPU性能上。”她说。

根据戴伟民博士的分享,目前AI-Pad的应用场景主要分为以下四种:

汪志伟认为,过去人们所谓的“智能教育”,其智能化程度是偏低的,因为过去属于硬件领先软件,现在则变成软件领先硬件,硬件能力相对于智能化需求是偏弱的。而要让AI-Pad在教育领域发挥作用,他建议一方面可以借助RISC-V这种开放、灵活、可扩展的CPU架构来扩展AI算力;另一方面,通过附加AI引擎和算力单元,让AI-Pad硬件方案或芯片方案更有竞争力。

同时,如果有智能化的评价系统,帮助小朋友和家长一步步地推导出解题过程,也会对于教育有更大的帮助。因为教育很多时候是为了解决问题,是一个提出并解答问题的过程。当前大部分教育软件都是直接给出答案,但并没有给出解题思路分析。

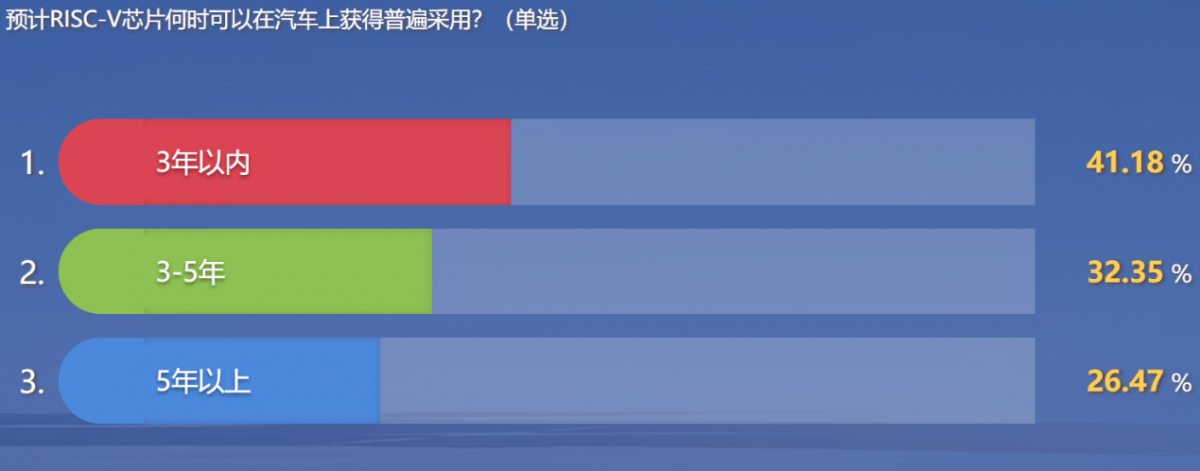

2024年6月24-28 日,2024 RISC-V欧洲峰会在德国慕尼黑举行,欧洲企业将RISC- V视为欧洲芯片设计崛起的最好机遇,几乎每一个国家都在增加RISC-V相关投入。全球各大汽车半导体知名厂商都在峰会上表达了对RISC-V上车的决心,英飞凌、博世、瑞萨、Quintauris等企业介绍了各自的产品进展与在汽车电子芯片领域的布局。

这其中,成立于2023 年 12 月 22 日,由高通、博世、英飞凌、恩智浦、北欧半导体(Nordic)共同投资组建的专注于RISC-V生态的初创企业Quintauris很引人关注。该公司总部位于德国慕尼黑,初期专注于为车用芯片,未来将扩大至包括手机及物联网等领域。

那么接下来,“汽车企业对RISC-V的接受度如何?高端车规芯片到底应该是SoC单芯片还是基于Chiplet的SiP?“

汪志伟先结合芯原实际畅谈了自己的看法。在他看来,第一代特斯拉FSD芯片只有36TOPS算力,如今已经来到500TOPS,未来可能需要更高的算力。从为了满足汽车电子领域对算力需求的角度来看,Chiplet技术是一个可能的解决方案。芯原跟RISC-V四大芯片厂中的两家都讨论过芯片相关的问题,包括可靠性、散热、安全等,已经取得了不错的进展,能够提供满足自动驾驶需求。的解决方案就要回到Chiplet上车的初衷是为了解决什么问题。”

“但无论在边缘端还是车端,目前最紧迫的还是AI算力不足的问题。“汪志伟表示,拓展算力需要在芯片中再额外添加一颗NPU和一颗AI ISP的Chiplet,借此带来300TOPS、500TOPS甚至1000TOPS的算力提升。因为有些芯片的AI算力最多只能支持6路、8路摄像头的AI计算,但现在新能源车上摄像头越来越多,12路已经很普遍。所以2颗-3颗Chiplet是针对自动驾驶比较现实可行的解决方案。

彭剑英以英飞凌为例,分享了RISC-V在汽车电子领域的进展。

“英飞凌此前的汽车芯片一直采用自研,但汇总各方面的消息,他们下一代ECU或车规平台就是基于定制化的RISC-V芯片。为什么英飞凌占据汽车半导体世界第一的位置,依然有决心投入RISC-V?”

彭剑英认为,汽车电子面临巨大转型,要从以前的相对封闭转变为软件定义汽车芯片。换句话说,“之前大家追求的是性能,例如MCU从16位升级到32位,现在强调的是软件和AI。如果不主动拥抱变化,会被市场抛弃。”

相比之下,因为RISC-V生态是一个开放的环境,它的可扩展性、可模块化适用于未来一颗芯片或整个汽车电子不同模块的芯片,都可以用同一个ISA、不同微架构实现的核心来统一满足需求。

以汽车ECU为例,系统管理配备一个核心,计算、加速器配备1-4个核心,AI-ECU则可能会有N个核心。如果只有一套软件生态,但是有不同的硬件实现可以满足不同的需求,这就是巨大的优势。虽然车载ECU对CPU的性能不再是简单地对标MCU,但会考虑到一系列的覆盖问题,这就不仅仅是IP选型的问题,而是整个软件生态兼容性的问题。

从芯来科技自身来看,公司自2021年开始做车规产品,从2021年9月到2023年7月份,NA900成为全球首个获得ISO 26262 ASIL D认证的RISC-V CPU IP产品,之后NA300系列也拿到了认证。目前搭载芯来ASIL-B和ASIL-D IP的芯片,已经应用于国内、国际头部的激光雷达、毫米波雷达产品并量产。

最前沿的电子设计资讯

最前沿的电子设计资讯