摘录自Christopher Paul的“Parsing PWM (DAC) performance: Part 1—Mitigating errors”:

“我很惊讶地发现,当我使用的一款常用µP的输出被配置为恒定逻辑低电平或高电平,并且仅由10MΩ输入数字万用表加载时,电压电平在某些情况下会超过电源电压VDD和地之间的100mV……我们称之为饱和误差。”

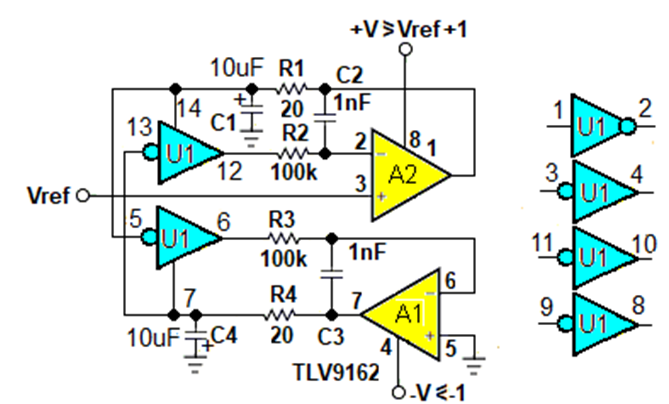

PWM DAC的精度取决于几个因素,但其中最重要的莫过于模拟开关元件能够可靠且精确地输出零电压和参考电压电平以响应相应的数字状态。然而,正如Christopher Paul设计实例中观察到的那样,有时它们并不会。这些偏差背后的机制尚不完全清楚,但如果能够可靠地消除它们,对PWM性能的影响一定是积极的。图1提出了一种强制修复的方法。

图1:U1是一个多极(例如,74AC04六反相器)PMW开关,其中运算放大器A1强制开关零状态以准确跟踪0=0V,运算放大器A2完成1=Vdd的工作。

U1引脚5与引脚14的连接会将引脚6驱动至逻辑0,由A1引脚6检测出。A1引脚7与U1引脚7的连接会强制将引脚6电压精确为零伏,从而当相关开关处于逻辑0时,强制所有U1输出为相同的精确零电平。

类似地,U1引脚13与引脚7的连接会将引脚12驱动至逻辑1,由A2引脚2检测出。A2引脚1与U1引脚14的连接会将引脚12电压强制精确为Vdd,从而当相关开关处于逻辑1时,强制所有U1输出为相同的精确Vref电平。

因此,任何现存的“饱和误差”都会被强制归零,不管它们实际上来自何处。

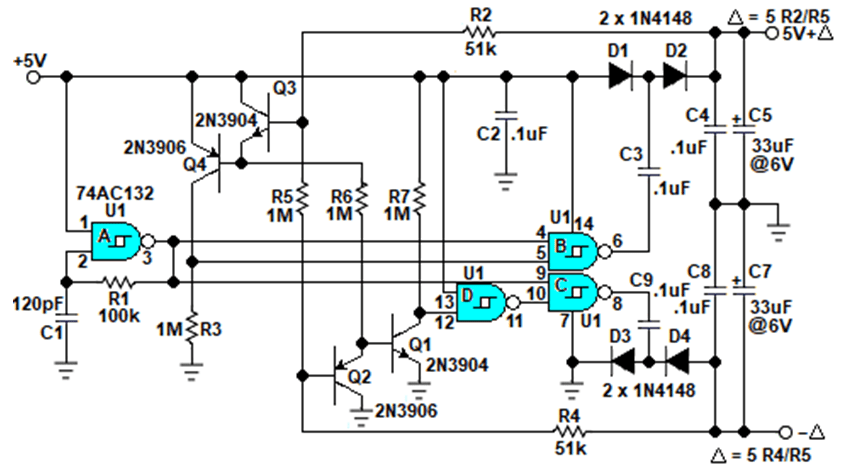

Vdd通常约为5.00V。V+和V-可通过任意数量的分立或单片轨道升压电路从单一的5V电源供电。图2是一种实际可行的方法。

图2:V+和V-的实用电源设置,R1和R2=200k,∆=1V。

图2中的电路最初在“一个高效数字调节双极电压轨升压器,电流效率最高99%”一文中有描述。

(原文刊登于EDN美国版,参考链接:Brute force mitigation of PWM Vdd and ground “saturation” errors,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯