最近有很多有趣的设计实例,将便宜的瞬时触点开关设计用在开/关电源控制电路上。

此类设计大多采用了边沿触发器(例如CD4013),但当然也存在其他可能的方案,图1就展示了其中一种。

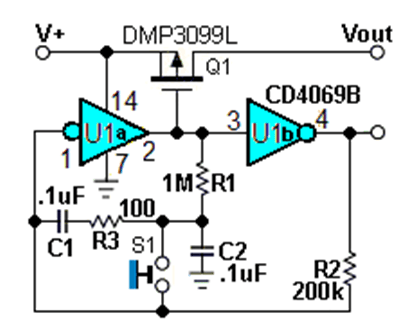

图1:无触发器/触发器去抖动的按压开关,具有上电复位功能,零件数量少。

从技术角度来说,将图1描述为无触发器电路并不准确,因为两个反相器U1a和U1b连接成双稳态锁存器,也就是说,它就是一个触发器,真正不同的是S1如何切换其状态。它的工作原理如下:

无论S1处于开启状态还是关闭状态,U1a作为反相器,都会通过R1将C2充电至相反状态。因此,当S1被触发时,C2会触发U1a的输入,从而触发锁存器。R1C2的时间常数为100毫秒,足以保证即使S1接通后发生反弹(这几乎是必然的),C2的互补电荷也能不受这一波动的影响。

然后,由于R2<R1,通过R2的正反馈将超过R1,只要S1保持闭合状态,C2上就会保持相同极性的电荷。这确保了之后S1释放时,即使它发生断路反弹(据说有些开关会这样),新的锁存状态也不会丢失,PFET Q1现在向负载传输电力(或者不传输),因此,我们可以放心地进行翻转和开启/关闭。

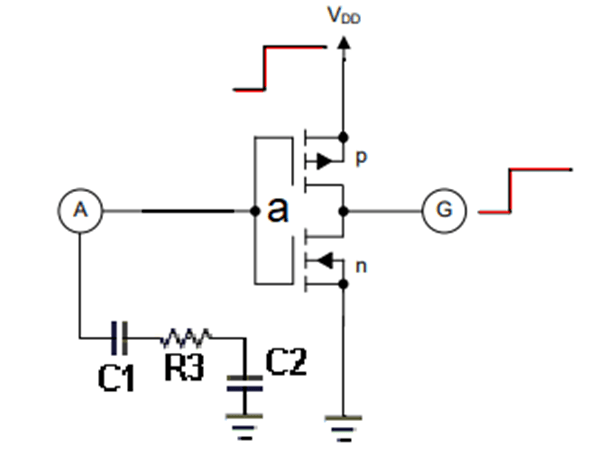

那么,C1的作用是什么呢?图2给出了解释。

图2:上电关闭时,PFET a源极的V+上升沿(其栅极由RC保持低位)将其打开。

图2:上电关闭时,PFET a源极的V+上升沿(其栅极由RC保持低位)将其打开。

如果V+电压处于零电平一段时间(例如电池取出或电源适配器被拔掉),C1和C2也会放电至零电平(或接近零电平)。因此,当V+电压恢复时,它们会将反相器的FET栅极保持在地电位,这将使PFET的栅极相对于其(上升沿)源极变为负电位,使其导通,将输出拉高,并将锁存器复位至OFF。

那么为什么是R3呢?

当锁存器在S1未按下的情况下(无论开启还是关闭)停留一段时间时,C1都会充电至V+,然后,当S1按下时(注意,这并不一定意味着它不正常),C1会“快速”放电。如果没有R3,“快速”放电可能适得其反,会导致S1瞬间电流过大,从而在其触点上沉积过多的能量,缩短其使用寿命。

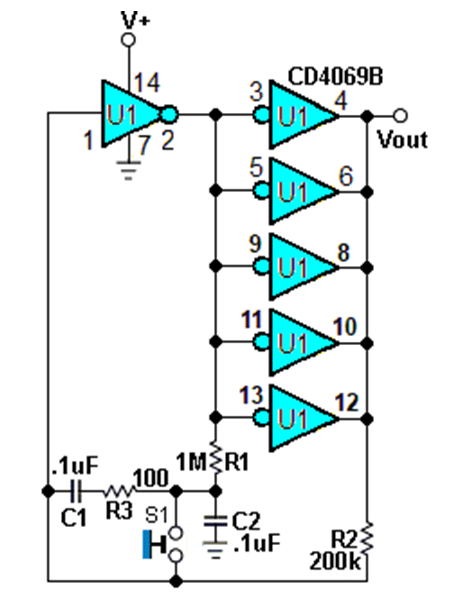

最后再说说关于元件数量的一些想法。4069是6反相器电路,但图1中六个反相器中只使用了两个,看起来有些浪费。我们希望设计人员能够在应用的其他地方找到未使用的元件的位置,但如果找不到呢?

那么图3可能会派上用场。

图3:利用U1的其余2/3做一些有用的事情,在负载小于10mA时取消Q1,并获得短路保护。

4069的Ron取决于V+,但在V+>10V时,其可低至200Ω(典型值)。因此,如果我们将所有五个可用的反相器并联,如图3所示,将获得从V+到Vout的净Ron为200/5=40Ω,这对于低功耗应用来说可能已经足够了,就用不上Q1了。此外,意外短路至地会迅速自动关闭锁存器并关闭短路负载,因此,U1起火的可能性会大大降低,从而减少我们的损失!请注意,即使锁存器关闭且输出短路至V+,此方法也同样有效。

(原文刊登于EDN美国版,参考链接:Flip ON flop OFF without a flip/flop,由Ricardo Xie编译)

最前沿的电子设计资讯

最前沿的电子设计资讯